# ZCC1699B Off-Line Digital Green-Mode Quasi-Resonant PWM Controller

# DIGITAL PWM IC

# 1.0 General Description

The ZCC1699B is a high performance AC/DC power supply controller which uses digital control technology to build peak current mode PWM flyback power supplies. The device operates in guasi-resonant mode to provide high efficiency along with a number of key built-in protection features while minimizing the external component count, simplifying EMI design and lowering the total bill of material cost. The ZCC1699B removes the need for secondary feedback circuit while achieving excellent line and load regulation. It also eliminates the need for loop compensation components while maintaining stability over all operating conditions. Pulse-by-pulse waveform analysis allows for a loop response that is much faster than traditional solutions, resulting in improved dynamic load response for both one-time and repetitive load transients. The built-in power limit function enables optimized transformer design in universal off-line applications and allows for a wide input voltage range. Hunch's innovative proprietary technology ensures that power supplies built with the ZCC1699B can achieve both highest average active efficiency and less than 30 mW no-load power consumption, and have fast dynamic load response in a compact form factor in typical 12 W and above applications. The active start-up scheme enables shortest possible start-up time without sacrificing no-load power loss.

#### Features

- No-load power consumption < 30 mW at 230 VAC along with fast dynamic load response and short turn-on delay time in typical 12 W compact adapter/charger applications

- Tight constant-voltage and constant-current regulation across line and load range

- Primary-side feedback eliminates opto-isolators and simplifies design

- Proprietary optimized 90 kHz maximum PWM switching frequency with quasi-resonant operation achieves best size, efficiency and common mode noise

- User-configurable 5-level cable drop compensation provides design flexibility

- Adaptive Multi-mode PWM/PFM control improves efficiency

- No external loop compensation components required

- Complies with CoC Version 5 Tier 2 and DOE level VI energy-efficiency specifications with ample margin Complies with EPA 2.0 energy-efficiency specifications with ample margin

- Built-in single-point fault protection features: output short-circuit protection, output over-voltage protection, over-current protection and current-sense-resistor fault protection

- Dedicated pins for external ver-temperature protection and over-voltage protection

- No audible noise over entire operating range

#### Applications

- Compact AC/DC adapter/chargers for media tablets and smart phones

- AC/DC adapters for consumer electronics

# **2.0** Products Information

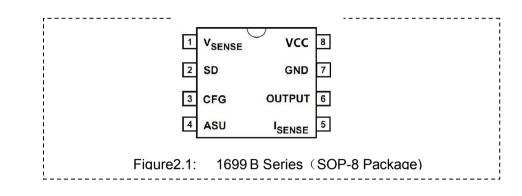

#### 2.1 Pin configuration

| Pin#  | Name               | I/O          | Description                                                                                                                           |

|-------|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>SENSE</sub> | Analog Input | Auxiliary voltage sense (used for primary regulation).                                                                                |

| 2     | SD                 | Analog Input | External shutdown control. Used for external over-temperature protection (OTP) by connecting an NTC resistor from this pin to Ground. |

|       |                    |              | Shared Multi-function pin. Used for external cable drop                                                                               |

| 3     | CFG                | Analog Input | compensation (CDC) configuration and supplemental                                                                                     |

|       |                    |              | over-voltage protection (OVP).                                                                                                        |

| 4 ASU |                    | Output       | Control signal for active start-up device (BJT or depletion                                                                           |

| 4     | ASU                | Output       | mode NFET).                                                                                                                           |

| 5     |                    |              | Primary current sense. Used for cycle-by-cycle peak current                                                                           |

| 5     | I <sub>SENSE</sub> | Analog Input | control and limit.                                                                                                                    |

| 6     | OUTPUT             | Output       | Gate drive for external MOSFET switch.                                                                                                |

| 7     | GND                | Ground       | Ground.                                                                                                                               |

| 8     | VCC                | Power Input  | Power supply for control logic.                                                                                                       |

#### 2.3 Series description

| Part Number | Description                              |  |  |  |  |

|-------------|------------------------------------------|--|--|--|--|

| ZCC1699B-02 | No OVP/OTP latch                         |  |  |  |  |

| ZCC1699B-03 | OVP/external OTP latch                   |  |  |  |  |

| ZCC1699B-05 | No OVP/OTP latch, 3V CC shutdown voltage |  |  |  |  |

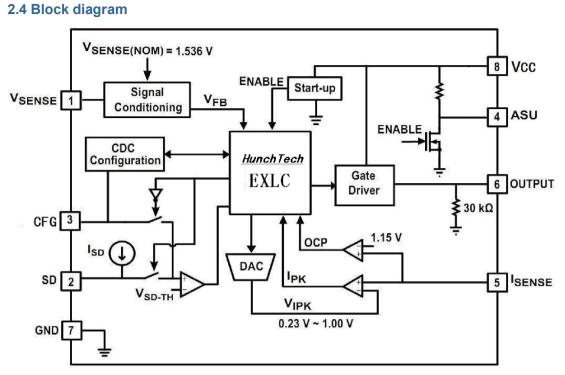

Figure2.1ZCC1699B Functional Block Diagram

# 3.0 Absolute Maximum Ratings

| Parameter                                                   | Symbol            | Value        | Units |

|-------------------------------------------------------------|-------------------|--------------|-------|

| DC supply voltage range (pin 8, I <sub>DD</sub> = 20mA max) | VCC               | -0.3 to 25.0 | V     |

| Continuous DC supply current at VCC pin<br>(VCC = 15 V)     | I <sub>DD</sub>   | 20           | mA    |

| ASU output (Pin 4)                                          |                   | -0.3 to 19.0 | V     |

| OUTPUT (Pin 6)                                              |                   | -0.3 to 20.0 | V     |

| V <sub>SENSE</sub> input (Pin 1, I <sub>VENSE</sub> ≤ 10mA) |                   | -0.7 to 4.0  | V     |

| ISENSE input (Pin 5)                                        |                   | -0.3 to 4.0  | V     |

| SD (pin2)                                                   |                   | -0.3 to 4.0  | V     |

| CFG(Pin 3, I <sub>CFG</sub> ≤ 20mA)                         |                   | -0.8 to 4.0  | V     |

| Maximum junction temperature                                | $T_{JMAX}$        | 150          | °C    |

| Operating junction temperature                              | T <sub>JOPT</sub> | -40 to 150   | °C    |

| Storage temperature                                         | T <sub>STG</sub>  | –65 to 150   | °C    |

| Lead temperature during IR reflow for $\leq$ 15 seconds     | $T_{LEAD}$        | 260          | °C    |

| Thermal resistance junction-to-ambient                      | $\theta_{JA}$     | 160          | °C/W  |

| ESD rating per JEDEC JESD22-A114                            |                   | 2,000        | V     |

| Latch-up test per JEDEC 78                                  |                   | ±100         | mA    |

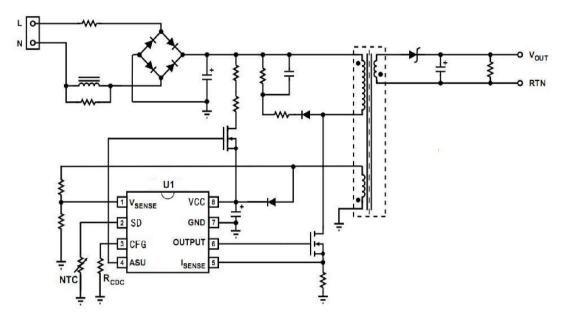

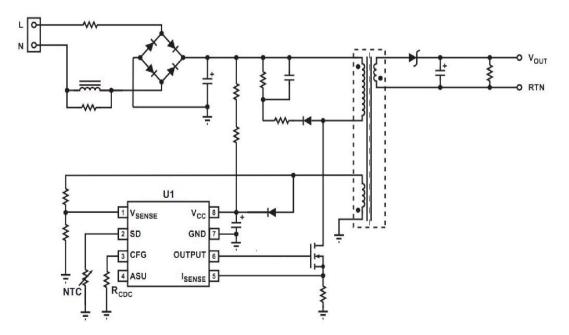

### 4.0 Typical Application

The ZCC1699B contains a controller for a flyback circuit.

Figure4.1ZCC1699B Typical Application Circuit(Achieving < 30 mW No-load Power Consumption)

Figure4.2ZCC1699B Typical Application (Alternative Circuit without Using Active Start-up Device)

# **5.0 Electrical Characteristics**

| (TA = 25°C, VCC=12V, | unless otherwise noted) |

|----------------------|-------------------------|

|----------------------|-------------------------|

| Symbol Parameter                  |                                                         | <b>Test Conditions</b>                                       | Min  | Тур   | Max  | Unit |  |  |

|-----------------------------------|---------------------------------------------------------|--------------------------------------------------------------|------|-------|------|------|--|--|

| SD SECTION(Pin2)                  |                                                         |                                                              |      |       |      |      |  |  |

| V <sub>SD-TH(F)</sub>             | Shutdown threshold<br>(falling edge)                    | -                                                            | 0.95 | 1.0   | 1.05 | V    |  |  |

| VSD-TH(ST_F)                      | Shutdown threshold<br>before start-up                   | -                                                            | 1.14 | 1.2   | 1.26 | V    |  |  |

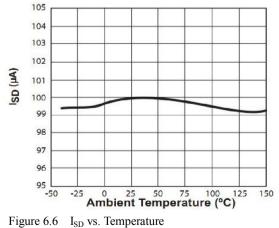

| I <sub>SD</sub>                   | Shutdown current source                                 | -                                                            | 95   | 100   | 105  | uA   |  |  |

| CFG Section (P                    | in3)                                                    |                                                              | •    |       | •    |      |  |  |

| $V_{\text{SD-TH}(R)}$             | OVP shutdown threshold<br>(rising edge)                 | - 0.96                                                       |      | 1.015 | 1.07 | V    |  |  |

| <b>OUTPUT Sectio</b>              | n (Pin6)                                                |                                                              |      |       |      | -    |  |  |

| R <sub>DS(ON)PD</sub>             | Driver pull-down<br>ON-resistance                       | I <sub>SINK</sub> = 5 mA                                     | -    | 12    | -    | Ω    |  |  |

| R <sub>DS(ON)</sub> PU            | Driver pull-up<br>ON-resistance                         | I <sub>SOURCE</sub> = 5 mA                                   | -    | 133   | -    | Ω    |  |  |

| t <sub>R</sub>                    | Rise time (Note 2)                                      | $T_A = 25^{\circ}C, C_L = 330 \text{ pF}$<br>10% to 90%      |      | 173   | -    | ns   |  |  |

| t <sub>F</sub>                    | Fall time (Note 2)                                      | T <sub>A</sub> = 25°C, C <sub>L</sub> = 330 pF<br>90% to 10% |      | 14    | -    | ns   |  |  |

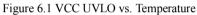

| f <sub>SW</sub>                   | Switching frequency<br>(Note 3)                         | > 50% load -                                                 |      | 90    | -    | kHz  |  |  |

| VCC SECTION (                     | Pin8)                                                   |                                                              |      |       |      |      |  |  |

| VCC <sub>(MAX)</sub>              | Maximum operating voltage (Note 2)                      | -                                                            | -    | -     | 20   | V    |  |  |

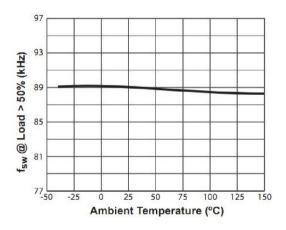

| VCC <sub>(ST)</sub>               | Start-up threshold                                      | VCC rising                                                   | 13.0 | 14.0  | 15.0 | V    |  |  |

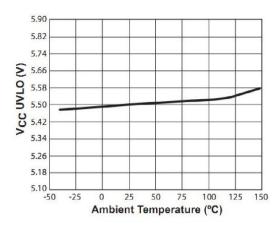

| VCC <sub>(UVL)</sub>              | VCC <sub>(UVL)</sub> Under-voltage lockout<br>threshold |                                                              | 5.2  | 5.5   | 5.8  | V    |  |  |

| VCC <sub>(RLS)</sub>              | VCC <sub>(RLS)</sub> Latch release threshold VCC f      |                                                              | 4.2  | 4.5   | 4.8  | V    |  |  |

| I <sub>IN(ST)</sub>               | Start-up current                                        | VCC = 12V                                                    | -    | 7.8   | -    | uA   |  |  |

| Iccq                              | Quiescent current                                       | $C_L$ =330pF, $V_{SENSE}$ =1.5V                              | -    | 3.5   | -    | mA   |  |  |

| ASU SECTION (Pin4)                |                                                         |                                                              |      |       |      |      |  |  |

| V <sub>ASU(MAX)</sub>             | Maximum operating voltage (Note 2)                      | -                                                            | -    | -     | 16   | V    |  |  |

| Resistance between VCC<br>and ASU |                                                         | -                                                            | -    | 1100  | -    | kΩ   |  |  |

| Symbol                  | Parameter                                                                              | <b>Test Conditions</b>   | Min   | Тур   | Max   | Unit |  |  |

|-------------------------|----------------------------------------------------------------------------------------|--------------------------|-------|-------|-------|------|--|--|

| V <sub>SENSE</sub> SECT | ION (Pin 1)                                                                            |                          |       |       |       |      |  |  |

| I <sub>BVS</sub>        | Input leakage current                                                                  | V <sub>SENSE</sub> = 2 V | -     | -     | 1     | uA   |  |  |

| V <sub>SENSE(NOM)</sub> | Nominal voltage threshold                                                              | TA=25°C, negative edge   | 1.521 | 1.536 | 1.551 | V    |  |  |

| V <sub>SENSE(MAX)</sub> | V <sub>SENSE</sub> -based output OVP<br>threshold with no CDC<br>compensation (Note 1) | TA=25°C, negative edge   | -     | 1.838 | -     | V    |  |  |

| ISENSE SECTI            | I <sub>SENSE</sub> SECTION (Pin 5)                                                     |                          |       |       |       |      |  |  |

| V <sub>OCP</sub>        | Over-current threshold                                                                 | -                        | 1.11  | 1.15  | 1.19  | V    |  |  |

| V <sub>IPK(HIGH)</sub>  | ISENSE regulation upper limit (Note 2)                                                 | -                        | -     | 1.0   | -     | V    |  |  |

| V <sub>IPK(LOW)</sub>   | ISENSE regulation lower<br>limit (Note 2)                                              | -                        | -     | 0.23  | -     | V    |  |  |

Notes:

Note 1: The  $V_{SENSE}$ -based output OVP threshold depends on the CDC setup, see Section 7.12 for more details.

Note 2: These parameters are not 100% tested, guaranteed by design and characterization.

Note 3: Operating frequency varies based on the load conditions, see Section 7.6 for more details

### 6. Typical Performance Characteristics

Figure 6.3 Switching Frequency vs. Temperature

Figure 6.5 VCC vs. VCC Supply Start-up Current

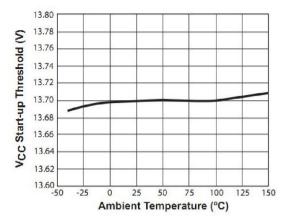

Figure 6.2 Start-Up Threshold vs. Temperature

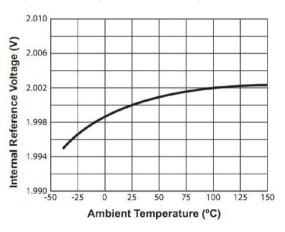

Figure 6.4 Internal Reference vs. Temperature

Notes:

### ZCC1699B

### **Off-Line Digital Green-Mode Quasi-Resonant PWM Controller**

Note1: Operating frequency varies based on the load conditions, see Section 7.6 for more details.

## 7. Theory of Operation

The ZCC1699B is a digital controller which uses a new, proprietary primary-side control technology to eliminate the opto-isolated feedback and secondary regulation circuits required in traditional designs. This results in a low-cost solution for low power AC/DC adapters. The core PWM processor uses fixed-frequency Discontinuous Conduction Mode (DCM) operation at higher power levels and switches to variable frequency operation at light loads to maximize efficiency. Furthermore, Our digital control technology enables fast dynamic response, tight output regulation, and full featured circuit protection with primary-side control.

Referring to the block diagram in Figure 2.1, the ZCC1699B operates in peak current mode control. The digital logic control block generates the switching on-time and off-time information based on the output voltage and current feedback signal and provides commands to dynamically control the external MOSFET gate voltage. The I<sub>SENSE</sub> is an analog input configured to sense the primary current in a voltage form. In order to achieve the peak current mode control and cycle-by-cycle current limit, the V<sub>IPK</sub> sets the threshold for the I<sub>SENSE</sub> to compare with, and it varies in the range of 0.23 V (typical) to 1.00 V (typical) under different line and load conditions. The system loop is automatically compensated internally by a digital error amplifier. Adequate system phase margin and gain margin are guaranteed by design and no external analog components are required for loop compensation. The ZCC1699B uses an advanced digital control algorithm to reduce system design time and increase reliability.

Furthermore, accurate secondary constant current operation is achieved without the need for any secondary-side sense and control circuits.

The ZCC1699B uses adaptive MULTI-mode PWM/PFM control to dynamically change the MOSFET switching frequency for efficiency,EMI,and power consumption optimization. In addition, it achieves unique MOSFET quasi-resonant switching to further improve efficiency and reduce EMI. Built-in single-point fault protection features include over-voltage protection (OVP), output short-circuit protection (SCP), over-current protection (OCP), and I<sub>SENSE</sub> fault detection. In particular, it ensures that power supplies built with the ZCC1699B can meet 5-star energy rating requirement and achieve fast dynamic load response in typical 12 W and above compact adapter/charger applications.

Our digital control scheme is specifically designed to address the challenges and trade-offs of power conversion design. This innovative technology is ideal for balancing new regulatory requirements for green mode operation with more practical design considerations such as lowest possible cost, smallest size and high performance output control.

#### 7.1 Pin Detail

$Pin \; 1 - V_{\text{SENSE}}$

Sense signal input from auxiliary winding. This provides the secondary voltage feedback used for output regulation..

Pin 2 – SD

External shutdown control. If the voltage at this pin is lower than 1.2 V (typical) at the beginning of start-up or lower than 1.0 V (typical) during normal operation, then the IC shuts down. Leave this pin unconnected if the shutdown control is not used (Refer to Section 7.14).

Pin 3 – CFG

MULTI-function pin. Used to configure external cable drop compensation (CDC) at the beginning of start-up and provide over-voltage protection during normal operation by sensing output voltage via auxiliary winding.

Pin 4 – ASU

Control signal for active startup device. This signal is pulled low after start-up is finished to cut off the active device.

Pin 5 – I<sub>SENSE</sub> Primary current sense. Used for cycle-by-cycle peak current control and limit..

Pin 6 – OUTPUT Gate drive for the external power MOSFET switch.

Pin 7 – GND Ground.

Pin 8 – VCC

Power supply for the controller during normal operation. The controller will start up when VCC reaches 14.0 V (typical) and will shut down when the VCC voltage drops below 5.5 V (typical). A decoupling capacitor of 0.1  $\mu$ F or so should be connected between the VCC pin and GND.

#### 7.2 Active Start-up and Soft-start

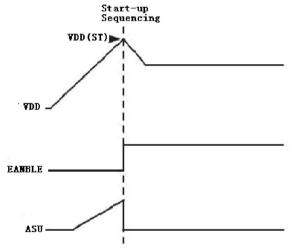

Refer to Figure 4.1 for active start-up circuit using external depletion mode NFET. Prior to start-up, the ENABLE signal is low, and the ASU pin voltage closely follows the VCC pin voltage, as shown in Figure 7.1. Consequently, the depletion mode NFET is turned on,

allowing the start-up current to charge the VCC bypass capacitor. When the VCC bypass capacitor is charged to a voltage higher than the start-up threshold  $VCC_{(ST)}$ , the ENABLE signal becomes active and the ZCC1699B begins to perform initial OTP check (See Section 7.14), followed by CDC configuration (See Section 7.12). Afterwards, the ZCC1699B commences soft-start function. During this start-up process an adaptive soft-start control algorithm is applied, where the initial output pulses will be small and gradually get larger until the full pulse width is achieved. The peak current is limited cycle by cycle by the  $I_{PEAK}$  comparator. If at any time the VCC voltage drops below under-voltage lockout (UVLO) threshold VCC<sub>(UVL)</sub> then the ZCC1699B goes to shutdown. At this time ENABLE signal becomes low and the VCC capacitor begins to charge up again towards the start-up threshold to initiate a new soft-start process.

While the ENABLE signal initiates the soft-start process, it also pulls down the ASU pin voltage at the same time, which turns off the depletion NFET, thus minimizing the no-load standby power consumption.

In applications where active start-up is not needed, the start-up resistor can be directly connected to the VCC pin without using the active start-up device, and the ASU pin can be left unconnected. Refer to Figure 4.2 for the application circuit.

Figure 7.1: Start-up Sequencing Diagram

### 7.3 Understanding Primary Feedback

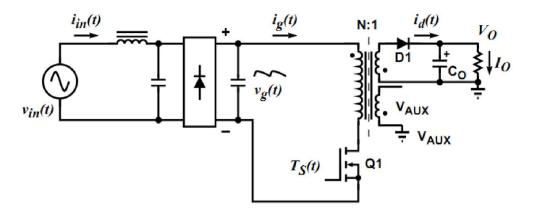

Figure 7.2 illustrates a simplified flyback converter. When the switch Q1 conducts during  $t_{ON}(t)$ , the current  $i_g(t)$  is directly drawn from rectified sinusoid  $v_g(t)$ . The energy  $E_g(t)$  is stored in the magnetizing inductance  $L_M$ . The rectifying diode D1 is reverse biased and the load current  $I_O$  is supplied by secondary capacitor  $C_O$ . When Q1 turns off, D1 conducts and the stored energy  $E_g(t)$  is delivered to the output.

Figure 7.2: Simplified Flyback Converter

In order to tightly regulate the output voltage, the information about the output voltage and load current need to be accurately sensed. In the DCM flyback converter, this information can be read via the auxiliary winding or the primary magnetizing inductance (L<sub>M</sub>). During the Q1 on-time, the load current is supplied from the output filter capacitor C<sub>0</sub>. The voltage across L<sub>M</sub> is v<sub>g</sub>(t), assuming the voltage dropped across Q1 is zero. The current in Q1 ramps up linearly at a rate of:

$$\frac{di_g(t)}{dt} = \frac{v_g(t)}{L_M}$$

(7.1)

At the end of on-time, the current has ramped up to:

$$i_{g_peak}(t) = \frac{v_g(t) \times t_{ON}}{L_M}$$

(7.2)

This current represents a stored energy of:

$$E_g = \frac{L_M}{2} \times i_{g_peak}(t)^2$$

(7.3)

When Q1 turns off at  $t_o$ ,  $i_g(t)$  in  $L_M$  forces a reversal of polarities on all windings. Ignoring the communication-time caused by the leakage inductance  $L_K$  at the instant of turn-off  $t_o$ , the primary current transfers to the secondary at a peak amplitude of:

$$i_d(t) = \frac{N_P}{N_S} \times i_{g_peak}(t)$$

(7.4)

Assuming the secondary winding is master, and the auxiliary winding is slave,

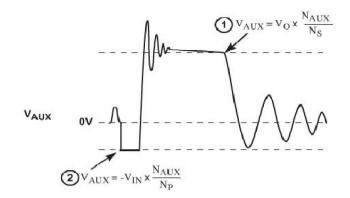

Figure 7.3: Auxiliary Voltage Waveforms

The auxiliary voltage is given by:

$$V_{AUX} = \frac{N_{AUX}}{N_s} (V_O + \Delta V)$$

(7.5)

and reflects the output voltage as shown in Figure 7.3.

The voltage at the load differs from the secondary voltage by a diode drop and IR losses. Thus, if the secondary voltage is always read at a constant secondary current, the difference between the output voltage and the secondary voltage will be a fixed  $\Delta V$ . Furthermore, if the voltage can be read when the secondary current is small,  $\Delta V$  will also be small. With the ZCC1699B,  $\Delta V$  can be ignored.

The real-time waveform analyzer in the ZCC1699B reads this information cycle by cycle. The part then generates a feedback voltage  $V_{FB}$ . The  $V_{FB}$  signal precisely represents the output voltage under most conditions and is used to regulate the output voltage.

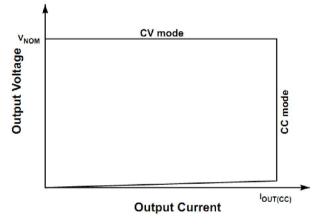

#### 7.4 Constant Voltage Operation

After soft-start has been completed, the digital control block measures the output conditions. It determines output power levels and adjusts the control system according to a light load or heavy load. If this is in the normal range, the device operates in the Constant Voltage (CV) mode, and changes the pulse width ( $T_{ON}$ ) and off time ( $T_{OFF}$ ) in order to meet the output voltage regulation requirements.

If no voltage is detected on  $V_{SENSE}$  it is assumed that the auxiliary winding of the transformer is either open or shorted and the ZCC1699B shuts down.

#### 7.5 Constant Current Operation

The constant current (CC) mode is useful in battery charging applications.During this mode of operation the ZCC1699B will regulate the output current at a constant level regardless of the output voltage, while avoiding continuous conduction mode.

To achieve this regulation the ZCC1699B senses the load current indirectly through the primary current. The primary current is detected by the  $I_{SENSE}$  pin through a resistor from the MOSFET source to ground.

The ZCC1699B also provides a product option to disable the CC mode operation. If the power supply enters into the CC mode during normal operation, this product option will shut down the power supply. This feature serves as an over-load protection and can be used in certain adapter applications.

Figure 7.4: Power Envelope

#### 7.6 MULTI-Mode PWM/PFM Control and Quasi-Resonant Switching

The ZCC1699B uses a proprietary adaptive MULTI-mode PWM /PFM control to dramatically improve the light-load efficiency and thus the overall average efficiency. During the constant voltage (CV) operation, the ZCC1699B normally operates in a pulse-width-modulation (PWM) mode during heavy load conditions. In the PWM mode, the switching frequency keeps around constant. As the output load  $I_{OUT}$  is reduced, the on-time  $T_{ON}$  is decreased, and the controller adaptively transitions to a pulse-frequency-modulation (PFM) mode. During the PFM mode, the MOSFET is turned on for a set duration under a given instantaneous rectified AC input voltage, but its off time is modulated by the load current. With a decreasing load current, the off time increases and thus the switching frequency decreases.

# ZCC1699B Off-Line Digital Green-Mode Quasi-Resonant PWM Controller

When the switching frequency approaches to human ear audio band, the ZCC1699B Transitions to a second level of PWM mode, namely Deep PWM mode (DPWM). During the DPWM mode, the switching frequency keeps around 25 kHz in order to avoid audible noise. As the load current is further reduced, the ZCC1699B transitions to a second level of PFM mode, namely Deep PFM mode (DPFM), which can reduce the switching frequency to a very low level. Although the switching frequency drops across the audible frequency range during the DPFM mode, the output current in the power converter has reduced to an insignificant level in the DPWM mode before transitioning to the DPFM mode. Therefore, the power converter practically produces no audible noise, while achieving high efficiency across varying load conditions.

As the load current reduces to very low or no-load condition, the ZCC1699B transitions from the DPFM to the third level of PWM mode, namely Deep-Deep PWM mode (DDPWM), where the switching frequency is fixed at around 1.8 kHz. The ZCC1699B also incorporates a unique proprietary quasi-resonant switching scheme that achieves valley-mode turn on for every PWM/PFM switching cycle, during all PFM and PWM modes and in both CV and CC operations. This unique feature greatly reduces the switching loss and dv/dt across the entire operating range of the power supply. Due to the nature of quasi-resonant switching, the actual switching frequency can vary slightly cycle by cycle, providing the additional benefit of reducing EMI. Together these innovative digital control architecture and algorithms enable the ZCC1699B to achieve highest overall efficiency and lowest EMI, without causing audible noise over entire operating range.

#### 7.7 Less Than 30 mW No-Load Power with Fast Load Transient Response

The ZCC1699B features a distinctive DDPWM control at no-load conditions to help achieve ultra-low no-load power consumption (< 30 mW for typical 12 W and above applications) and meanwhile to ensure fast dynamic load response. The power supply system designs including the pre-load resistor selection should ensure the power supply can operate in the DDPWM mode at the steady-state no-load condition. If the pre-load resistor is too small, the no-load power consumption will increase; on the other hand, if it is too large, the output voltage may increase and even cause over-voltage since the switching frequency is fixed at around 1.8 kHz. For typical designs, the pre-load resistor is in the range of 3 k  $\Omega$ .

Aside from the appropriate use of pre-load resistor, the ZCC1699B enjoys a few other features to bring down no-load power consumption as well. First, the ZCC1699B implements an intelligent low-power management technique that achieves ultra-low chip operating current at the no-load, typically less than 350  $\mu$ A. Second, a low UVLO threshold of 5.5 V (typical) enables the power supply system design to have a low VCC voltage at the

no-load operation in order to minimize the no-load power. In addition, the active start-up scheme with depletion mode NFET eliminates the start-up resistor power consumption after the ENABLE signal becomes active. All together these features ensure lowest system cost power supplies built with the ZCC1699B can achieve less than 30 mW no-load power consumption at 230 VAC input, and very tight constant voltage and constant current regulation over the entire operating range in typical 12 W and above compact adapter/charger applications.

While achieving ultra-low no-load power consumption, the ZCC1699B implements innovative proprietary digital control technology to intelligently detect any load transient events, and achieve fast dynamic load response for both one-time and repetitive load transients. In particular, for load transients that are demanded in some applications from no load to full

load, theZCC1699B can still maintain a fast enough response to meet the most stringent requirements, with the no-load operating frequency designed at around 1.8 kHz.

#### 7.8 Variable Frequency Operation Mode

At each of the switching cycles, the falling edge of  $V_{SENSE}$  will be checked. If the falling edge of  $V_{SENSE}$  is not detected, the off-time will be extended until the falling edge of  $V_{SENSE}$  is detected. The maximum allowed transformer reset time is 110 µs. When the transformer reset time reaches 110 µs, theZCC1699B shuts off.

#### 7.9 Internal Loop Compensation

TheZCC1699B incorporates an internal Digital Error Amplifier with no requirement for external loop compensation. For a typical power supply design, the loop stability is guaranteed to provide at least 45 degrees of phase margin and -20 dB of gain margin.

#### 7.10 Voltage Protection Features

The secondary maximum output DC voltage is limited by theZCC1699B. When the  $\underbrace{\mathcal{H}_{NSE}}_{SE}$  signal exceeds the output OVP threshold at point 1 indicated in Figure 7.3 theZCC1699B shuts down. For this V<sub>SENSE</sub>-based OVP, latch function is available by product options given in Section 2.3.

TheZCC1699B protects against input line under-voltage by setting a maximum  $J_N$  time. Since output power is proportional to the squared  $V_{IN}T_{ON}$  product, then for a given output power, as  $V_{IN}$  decreases the  $T_{ON}$  will increase. Thus by knowing when the maximum  $T_{ON}$  time occurs theZCC1699B detects that the minimum  $V_N$  is reached, and shuts down. The

# ZCC1699B

### **Off-Line Digital Green-Mode Quasi-Resonant PWM Controller**

maximum  $t_{ON}$  limit is set to 13.8 µs. Also, the ZCC1699B monitors the voltage on the VCC pin

and when the voltage on this pin is below UVLO threshold the IC shuts down immediately.

When any of these faults are met the IC remains biased to discharge the VCC supply. Once VCC drops below UVLO threshold, the controller resets itself and then initiates a new soft-start cycle. The controller continues attempting start-up until the fault condition is removed. For the latched OVP version, the controller can only start-up when the fault is removed and input is unplugged to allow VCC to drop 1.0 V below UVLO threshold.

#### 7.11 PCL, OCP and SRS Protection

Peak-current limit (PCL), over-current protection (OCP) and sense-resistor-short protection (SRSP) are features built-in to the ZCC1699B.With the  $\underline{e}_{NSE}$  pin the ZCC1699B is able to monitor the peak primary current. This allows for cycle-by-cycle peak current control and limit. When the peak primary current multiplied by the  $I_{SENSE}$  resistor is greater than 1.15 V,over-current is detected and the IC will immediately turn off the gate driver until the next cycle. The output driver will send out a switching pulse in the next cycle, and the switching pulse will continue if the OCP threshold is not reached; or, the switching pulse will turn off again if the OCP threshold is reached. If the OCP occurs for several consecutive switching cycles, the ZCC1699B shuts down.

If the I<sub>SENSE</sub> resistor is shorted there is a potential danger that over-current condition may not be detected. Thus, the IC is designed to detect this sense-resistor-short fault after start-up and shut down immediately. The VCC will be discharged since the IC remains biased. Once VCC drops below the UVLO threshold, the controller resets itself and then initiates a new soft-start cycle. The controller continues attempting to startup, but does not fully start-up until the fault condition is removed.

#### 7.12 CDC Configuration

The ZCC1699B incorporates an innovative approach to allow users to configure cable drop compensation (CDC) externally. This configuration is only performed once. It is completed after the initial OTP check but before the soft-start commences. During the CDC configuration, the internal digital control block senses the external resistance value between the CFG pin and ground, and then sets a corresponding CDC level to allow the device to compensate for IR drop in the secondary circuitry during normal operation.

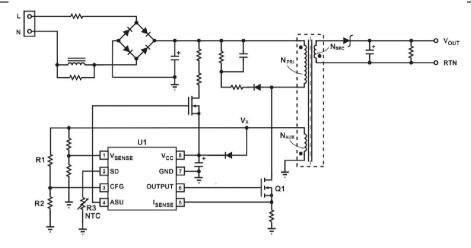

Figure 4.1 shows a simple circuit to set CDC level by connecting a resistor,  $R_{CDC}$ , from

# ZCC1699B

### **Off-Line Digital Green-Mode QR PWM Controller**

the CFG pin to ground. The ZCC1699B provides five levels of CDC configurations: 0, 75 mV, 150 mV, 300 mV, and 450 mV. Table 7.1 below shows the resistance range for each

of the five CDC levels. In practice, it is recommended to select resistance in the middle of the range wherever possible.

The "Cable Comp" specified in Table 7.1 refers to the voltage increment at PCB end from no-load to full-load conditions in the CV mode, with the assumption that the secondary diode voltage drop can be ignored at the point when the secondary voltage is sensed. Also, the "Cable Comp" is specified based on the nominal output voltage of 5 V. For different output voltage, the actual voltage increment needs to be scaled accordingly. To calculate the amount of cable compensation needed, take the resistance of the cable and connector and multiply by the maximum output current.

For each of the CDC levels, the internal  $V_{SENSE}$ -based OVP thresholds are different. Table 7.1 also lists the typical OVP thresholds for each CDC level.

|                                                         |        | <b>U</b>    | 0           | •         |           |

|---------------------------------------------------------|--------|-------------|-------------|-----------|-----------|

| CDC Level                                               | 1      | 2           | 3           | 4         | 5         |

| $R_{\text{CDC}}  \text{Range}  \left( k \Omega \right)$ | 0-2.20 | 2.37 – 3.21 | 3.40 - 4.64 | 4.87–6.65 | 6.98 – X* |

| Cable Comp (mV)                                         | 0      | 75          | 150         | 300       | 450       |

| V <sub>SENSE</sub> -based OVP<br>Threshold              | 1.838  | 1.861       | 1.884       | 1.930     | 1.976     |

Table7.1 Recommended resistance range and corresponding CDC levels for 5V output

\* The resistance can be as high as  $100k\Omega$ , provided CFG pin does not float, which causes device to shut down.

#### 7.13 External CFG-Based OVP

In the ZCC1699B, the CFG pin can also be used to provide the external over-voltage protection (OVP) besides fulfilling the CDC configuration. This external CFG-based OVP serves as a supplemental or extra protection in addition to the V<sub>SENSE</sub>-based OVP. The circuit implementation can be found in Figure 7.5, where two resistors R1 and R2 form a voltage divider to sense output voltage via auxiliary winding, with the tapping point connected to the CFG pin. During the CDC configuration the ZCC1699B does not send out any drive signal at OUTPUT pin, and the switch Q1 remains in off-state. The resistors R1 and R2 are essentially connected in parallel since the bias winding is virtually shorted. Consequently, the paralleled resistance of R1 and R2 sets the CDC level. Meanwhile, during normal operation, the CFG pin reflects output voltage in real-time, in the similar fashion as the V<sub>SENSE</sub> does at point 1 in Figure 7.3. The ratio of R1 to R2 sets the external OVP threshold.

# ZCC1699B Off-Line Digital Green-Mode Quasi-Resonant PWM Controller

The resistance values for the resistor divider, R1 and R2, can be derived as follows. First, for the given CDC level, the paralleled resistance of R1 and R2 should be within the

range listed in Table 7.1:

$$R_{CDC} = \frac{R_1 \times R_2}{R_1 + R_2}$$

(7.6)

Second, during normal operation the voltage divider, R1 and R2, sets the desired OVP threshold:

$$\left(\frac{N_{AUX}}{N_{SEC}}\right) \times V_{OVP} \times \left(\frac{R_2}{R_2 + R_1}\right) \ge V_{SD-TH(R)} \quad (7.7)$$

where NAUX is the number of turns for the bias winding,  $N_{SEC}$  is the number of turns for the secondary winding,  $V_{OVP}$  is the desired OVP tripping point, and  $V_{SD-TH(R)}$  is the internal comparator threshold (1.015 V typically) for OVP detection. The combination of Equations (9.6) and (9.7) leads to

$$R_{1} = \left(\frac{N_{AUX}}{N_{SEC}}\right) \times R_{CDC} \times \left(\frac{V_{OVP}}{V_{SD-TH(R)}}\right)$$

$$R_{2} = \left(\frac{R_{1}}{R_{1} - R_{CDC}}\right) \times R_{CDC}$$

(7.8)

It is recommended the  $R_{CDC}$  value is taken as the median value of the resistance range as given in Table7.1, and R1 and R2 can then be readily derived from Equation (7.8). It should be noted when the CFG pin is used to provide external OVP, an additional constraint will be applied to the resistance range given in Table7.1. Since for the OVP configuration in Figure 7.5, a large negative voltage may occur to the auxiliary winding (V<sub>x</sub> in Figure 7.5) during the switch on-time, which can cause a negative current flowing out of the CFG pin. Care needs to be taken to ensure R1 and R2 are large enough, so that the resulting negative current is less than the maximum allowed current, specified in Section 3.0.

# Off-Line Digital Green-Mode QR PWM Controller

Figure 7.5: Typical Application Circuit with CDC, OVP and OTP Implemented

#### 7.14 External OTP

The ZCC1699B can be configured to provide external over-temperature protection (OTP) by connecting a Negative-Temperature-Coefficient (NTC) resistor from SD pin to GND. Internally, a 100  $\mu$ A current source is injected to the SD pin, which generates a voltage proportional to the NTC resistance. At high ambient temperature, the NTC resistance becomes low, which results in a low voltage at the SD pin. If the SD pin voltage drops below an internally-set threshold, then the OTP is triggered, and the ZCC1699B shuts down.

In the ZCC1699B, the external OTP has a built-in hysteresis by having two thresholds. Before start-up, the OTP is triggered if the SD pin voltage is less than 1.2 V; otherwise the device begins the CDC configuration (See Section 7.12), then followed by a normal soft-start process. During normal operation, the OTP threshold is switched to 1.0 V, and the device only shuts down when the SD pin voltage is less than 1.0 V.

During normal operation, the external OVP and OTP detections alternate every eight cycles. During the eight-cycle window of OVP detection, the voltage at the CFG pin is fed into the internal comparator's non-inverting input. If the voltage of this pin is above 1.015 V at the instant corresponding to point 1 indicated in Figure 7.3 for consecutive several cycles, then OVP is triggered. Contrarily, during the external OTP detection window, if the voltage at SD pin is below 1.0 V for consecutive several cycles, then the OTP is triggered, and the device shuts down.

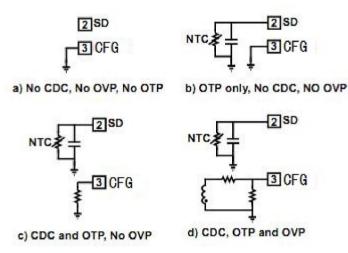

The SD pin and CFG pin can be configured to provide different types of applications. Figure 7.6 shows four basic configurations:

In Scheme (a), the CFG pin is directly connected to ground, which sets CDC level to be 1

# ZCC1699B

### Off-Line Digital Green-Mode Quasi-Resonant PWM Controller

(i.e. no CDC). On the other side, leaving the SD pin unconnected disables the OTP function.

In Scheme (b), CDC is set to level 1, as in Scheme (a) by grounding the CFG pin. An NTC resistor in paralleled with a capacitor enables the external OTP protection. Note this capacitor is only for decoupling purpose. Its capacitance needs to be less than 47 pF, otherwise the voltage at this pin can be delayed too much, causing unwanted behaviors.

In Scheme (c), a resistor from the CFG pin to ground allows to set the desired CDC level. Similarly, the NTC resistor enables the external OTP, as in Scheme (b).

In Scheme (d), the connections to the CFG and the SD pins are complete as in Figure 7.5, allowing for any level of CDC configuration, and meanwhile enabling the external OTP and OVP.

Figure 7.6: CFG and SD Pins Configurations

#### 7.15 Latch and Release

In the ZCC1699B, both OTP and OVP (including V<sub>SENSE</sub>-based and the external Mulit-based OVP) can be latched whereby the ZCC1699B does not attempt to start again even with the fault cleared. In the latch state, the controller recycles itself by periodically ramping VCC up and down between VCC(ST) and VCC(UVL), and the controller will not start up, provided the input stays connected to the AC source. To get out of the latch state, unplugging the input from the AC source is required, so that the VCC is allowed to

drop 1.0 V below VCC(UVL) to release the latch.

For a fast release, VCC capacitor can be charged directly from the AC source before the diode-bridge rectifier instead of the bulk capacitor. In this way, when the input is unplugged, the VCC capacitor is immediately cut off from the bulk capacitor, allowing for much faster discharging to release the latch, and initiate a normal start-up thereafter.

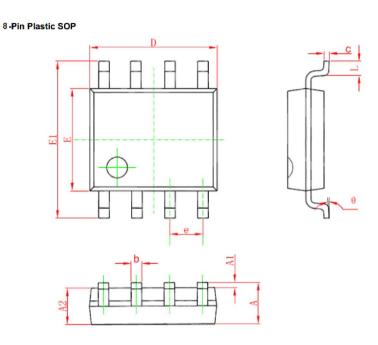

# 8. Package Information

#### SOP-8

| Symbol | Dimension in | n Millimeters | Dimensions in Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| A      | 1.350        | 1.750         | 0.053                | 0.069 |  |

| A1     | 0.050        | 0.250         | 0.002                | 0.010 |  |

| A2     | 1.250        | 1.650         | 0.049                | 0.065 |  |

| b      | 0.310        | 0.510         | 0.012                | 0.020 |  |

| С      | 0.100        | 0.250         | 0.004                | 0.010 |  |

| D      | 4.700        | 5.150         | 0.185                | 0.203 |  |

| E      | 3.800        | 4.000         | 0.150                | 0.157 |  |

| E1     | 5.800        | 6.200         | 0.228                | 0.244 |  |

| е      | 1.270(BSC)   |               | 0.050(BSC)           |       |  |

| L      | 0.400        | 1.270         | 0.016                | 0.050 |  |

| θ      | 0°           | 8°            | 0°                   | 8°    |  |