# High Performance Synchronous CV/CC Buck Converter with Dual Outputs

### **General Description**

AP2963 is a High Efficiency, Dual Outputs Synchronous DC-DC Buck Converters with CV/CC modes, which can output up to 21W in a wide range input from 6 V to 38 V. AP2963 operates either in Constant Output Voltage (CV) mode or Constant Output Current (CC) mode and provides a separated current limit function for each channel. In order to achieve better EMI performance and comply with Apple's MFi standard, the switching frequency was fixed at 125 kHz. AP2963 is capable to operate in CC mode down to 3 V output voltage to protect the soft-short condition that is from the over current of the portable device

Other features including output Over Voltage Protection (OVP), soft-start, hiccup mode output Under Voltage Protection (UVP), thermal shutdown (TSD), input UVLO. The hiccup mode output UVP can reduce the average input current to 50 mA. AP2963 is available in SOP8-EP packages which is beneficial for compact solution as well as thermal dissipation.

### **Applications**

- Car Charger

- Portable Charging Devices

- CV/CC regulation DC/DC converter

### **Features**

- Wide Range Input Supply Voltage from 6 V -38 V

- Output Current up to 4.2A

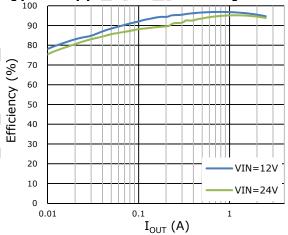

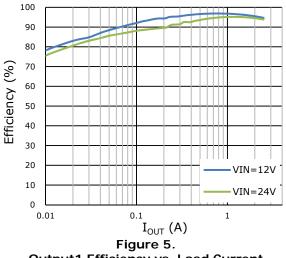

- High Efficiency up to 92 %

- Easy EMI design, 125 kHz Fixed Switching Frequency

- Internal Soft-Start Circuitry

- Built-in Input OVP, UVLO

- Compensation for Output Cord Voltage Drop

- Adjustable Constant Current Limits

- Output Over Voltage Protection

- Hiccup Mode Output UVP for Soft-short < 3 V

- Thermal Shutdown

- Thermally Enhanced SOP8-EP Package

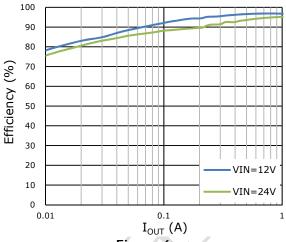

### Typical Application Efficiency

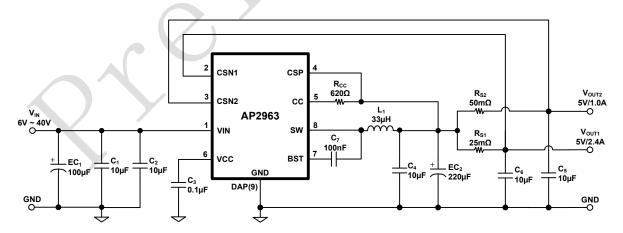

### **Typical Application Circuit**

**Ordering Information**

| Order Code | Shipping Top Marking |                                |  |

|------------|----------------------|--------------------------------|--|

| AP2963SPER | TBD/Reel             | AP2963<br>YYWWP <sup>(1)</sup> |  |

(1). YYWW = Date code, P = Assembly site

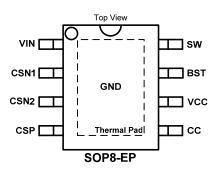

### **Pin Configuration**

**Pin Description**

| FIII Descri | Ottori       |                                                                                                                                                 |  |  |  |  |  |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No.     | Pin<br>Names | Pin Functions                                                                                                                                   |  |  |  |  |  |

| 1           | VIN          | Input Voltage Supply. Connect a decoupling capacitor between VIN and GND pins with least distance.                                              |  |  |  |  |  |

| 2           | CSN1         | Channel 1 Current Limit Negative Feedback pin. Kevin sensing from this pin to the sensing resistor is recommended.                              |  |  |  |  |  |

| 3           | CSN2         | Channel 2 Current Limit Negative Feedback pin. Kevin sensing from this pin to the sensing resistor is recommended.                              |  |  |  |  |  |

| 4           | CSP          | Current Limit Common and Output Voltage Feedback pin. Kevin sensing from this pin to the center point of both sensing resistors is recommended. |  |  |  |  |  |

| 5           | СС           | Cable Compensation pin. Connect a resistor to CSP to adjust cord compensation gain.                                                             |  |  |  |  |  |

| 6           | VCC          | Internal 5 V Power Supply. Connect a 100nF capacitor between VCC and GND pins for stability and noise de-coupling;                              |  |  |  |  |  |

| 7           | BST          | Boot-Strap pin. Supply input for the gate drive circuit of high-side NFET. Connect a 100nF capacitor between BST and SW pins.                   |  |  |  |  |  |

| 8           | SW           | Switch Node between high-side NFET and low-side NFET. Connect this pin to the switching node of inductor.                                       |  |  |  |  |  |

| DAP(9)      | GND          | Ground and Thermal Pad on the bottom of IC. Ground pin of internal circuitry and Power Return Pin for Sync-NFET source connection.              |  |  |  |  |  |

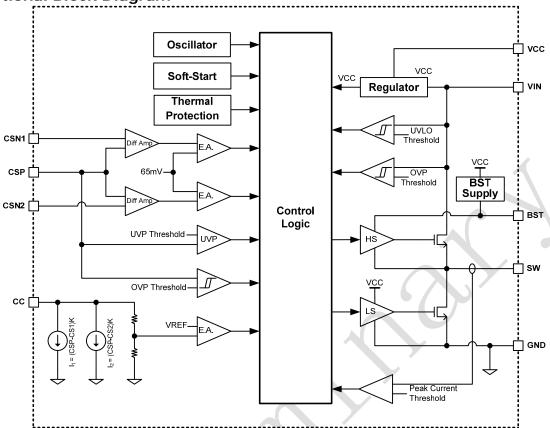

**Functional Block Diagram**

Figure 1. Functional Block Diagram

| (1)                                                  |                                                  |

|------------------------------------------------------|--------------------------------------------------|

| Absolute Maximum Ratings (                           |                                                  |

| VIN0.3 V ~ 42 V                                      | Θ <sub>JA</sub> TBD°C/W                          |

| SW0.3 V $\sim$ (V <sub>IN</sub> + 0.2 V) $\leq$ 42 V | Min. Operating T <sub>1</sub> 40 °C              |

| BST to SW0.3 V $\sim$ 6 V                            | Max. Operating T <sub>1</sub> Internally Limited |

| CSP, CSN1, CSN2, CC0.3 V ~ 6 V                       | Storage Temperature55 °C ~ 150 °C                |

| VCC0.3 V ~ 6 V                                       | Lead Temperature (Soldering 10 sec.)260 °C       |

| ESD Rating (Human Body Model)±4 kV <sup>(2)</sup>    |                                                  |

| Package Thermal Resistance <sup>(3)</sup>            |                                                  |

- (1). All voltages refer to GND pin unless otherwise noted; Stresses exceed those ratings may damage the device.

- (2). Tested and classified as Class 3A per ESDA/JEDEC JDS-001-2014.

- (3). Thermal Resistance is measured in the natural convection at  $T_A = 25$  °C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

### Electrical Characteristics (1)

$(V_{IN} = 12V, T_A = 25^{\circ}C, \text{ unless otherwise noted.})$

| Parameter                            | Parameter Symbol Conditions |                                                                                                                          | Min  | Тур | Max  | Unit |

|--------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Input Supply Voltage                 |                             |                                                                                                                          |      |     |      |      |

| Input Voltage                        | $V_{\rm IN}$                |                                                                                                                          | 6    |     | 38   | V    |

| Input UVLO & OVP                     |                             |                                                                                                                          |      | 7   |      |      |

| UVLO Threshold                       | V <sub>UVLO</sub>           | V <sub>IN</sub> Rising                                                                                                   | TBD  | 4.5 | TBD  | V    |

| UVLO Hysteresis                      | V <sub>UVLOHYS</sub>        | V <sub>IN</sub> Falling                                                                                                  |      | 500 |      | mV   |

| OVP Threshold                        | $V_{IN_{OVP}}$              | V <sub>IN</sub> Rising                                                                                                   | 37   | 38  | 39   | V    |

| OVP Hysteresis                       | V <sub>IN_OVPHYS</sub>      | V <sub>IN</sub> Falling                                                                                                  |      | 1   |      | V    |

| Input Supply Current                 |                             |                                                                                                                          |      |     |      |      |

| Quiescent Current(non-<br>switching) | $I_Q$                       | $V_{OUT} = 5.3 \text{ V}$                                                                                                |      | 500 | 1000 | μΑ   |

| Output Voltage                       |                             |                                                                                                                          |      |     |      |      |

| Output Voltage Regulation            | $V_{CSP}$                   | No Load                                                                                                                  | 5.0  | 5.1 | 5.2  | V    |

| CSP OVP Upper Threshold              | $V_{OVP}$                   | V <sub>CSP</sub> Rising                                                                                                  | 5.6  | 5.8 | 6    | V    |

| CSP OVP Hysteresis                   | V <sub>OVP_HYS</sub>        | V <sub>CSP</sub> Falling                                                                                                 |      | 100 |      | mV   |

| CSP OVP delay                        | $T_{OVP\_DLY}$              |                                                                                                                          |      | 200 |      | ns   |

| CSP UVP Threshold                    | $V_{UVP}$                   |                                                                                                                          | 2.25 | 2.5 | 2.75 | V    |

| UVP Hiccup Interval                  | $T_UVP$                     |                                                                                                                          |      | 1   |      | S    |

| Cable Compensation Voltage           | V                           | $R_{CC} = 620 \ \Omega,$ $I_{LOAD\_CH1} = 2.4 \ A,$ $I_{LOAD\_CH2} = 0 \ A,$ $R_S = 25 \ m\Omega$                        |      | 155 |      | mV   |

| Cable Compensation Voltage           | $V_{CCOMP}$                 | $\begin{split} R_{CC} &= 620~\Omega, \\ I_{LOAD\_CH1} &= 0~A, \\ I_{LOAD\_CH2} &= 1~A, \\ R_S &= 50~m\Omega \end{split}$ |      | 129 |      | mV   |

| Oscillator                           |                             |                                                                                                                          |      |     |      |      |

| Switching Frequency                  | $F_{SW}$                    | $I_{LOAD} = 0.1 A$                                                                                                       | 105  | 125 | 145  | kHz  |

| Maximum Duty Cycle                   | $D_{MAX}$                   |                                                                                                                          |      | 99  |      | %    |

| Minimum ON time                      | $T_{ONMIN}$                 |                                                                                                                          |      | 120 |      | ns   |

| MOSFET                               |                             |                                                                                                                          |      |     |      |      |

| High Side MOSFET On<br>Resistance(1) | $R_{DS(ON)H}$               |                                                                                                                          |      | 40  |      | mΩ   |

| Low Side MOSFET On<br>Resistance(1)  | R <sub>DS(ON)L</sub>        |                                                                                                                          |      | 30  |      | mΩ   |

| High-Side MOSFET Leakage<br>Current  | $I_{LEAK\_H}$               | $V_{SW} = 0 V$                                                                                                           |      |     | 10   | μΑ   |

| Parameter                                     | Symbol              | Conditions                     | Min  | Тур | Max  | Unit |

|-----------------------------------------------|---------------------|--------------------------------|------|-----|------|------|

| Low-Side MOSFET Leakage<br>Current            | I <sub>LEAK_L</sub> | $V_{SW} = V_{IN}$              |      |     | 10   | μΑ   |

| Current Limit                                 |                     |                                |      |     |      |      |

| High Side MOSFET Peak<br>Current Limit        | I <sub>LIM_HS</sub> | V <sub>OUT</sub> = 5 V         | 6    | 6.3 | 6.6  | А    |

| Channel 1 Constant Current<br>Limit Threshold | $I_{CS1}$           | $R_{CS1} = 25 \text{ m}\Omega$ | 2.47 | 2.6 | 2.73 | А    |

| Channel 2 Constant Current<br>Limit Threshold | I <sub>CS2</sub>    | $R_{CS2} = 50 \text{ m}\Omega$ | 1.28 | 1.3 | 1.31 | Α    |

| Regulator                                     |                     |                                |      |     |      |      |

| VCC Regulator                                 | $V_{CC}$            | $I_{LOAD} = 5 \text{ mA},$     | 4.9  | 5   | 5.1  | V    |

| VCC Current Limit                             | $I_{LIM\_VCC}$      |                                |      | 20  |      | mA   |

| Soft-start                                    |                     |                                |      |     |      |      |

| Soft-start Time                               | T <sub>SS</sub>     |                                |      | 2   |      | ms   |

| Thermal Shutdown                              |                     |                                |      |     |      |      |

| Thermal Shutdown threshold <sup>(1)</sup>     | T <sub>SDN</sub>    |                                |      | 165 |      | °C   |

| Thermal Shutdown<br>Hysteresis <sup>(1)</sup> | T <sub>SDNHYS</sub> |                                |      | 30  |      | °C   |

- (1). Specifications over temperature range are guaranteed by design and characterization.

- (2). Guaranteed by design and characterization only.

# Chipown

### **Functional Descriptions**

### Operation

The AP2963 is a monolithic high efficiency synchronous CV / CC buck converter with dual outputs. It utilizes internal MOSFETs to achieve high efficiency and up to 4.2 A output current in a wide input range from 6 V to 40 V. The constant current limit thresholds for each output can be programed through the CSP, CSN1 and CSN2 pins individually. The AP2963 is capable to operate in CC mode down to 3 V output voltage to protect the soft-short condition that is from the over current of the portable device.

With the slope compensated current mode PWM control, provides stable switching and cycle-by-cycle current limit for excellent load and line responses and protection of the internal switches. During normal operation, the internal main switch is turned on for a certain time to ramp up the inductor current at each rising edge of the internal oscillator, and turned off when the peak inductor current is above the error voltage. The current comparator limits the average inductor current. Once the main switch is turned off, the synchronous rectifier will be turned on immediately and stay on until either the inductor current decay to zero, as indicated by the zero current comparator or the beginning of the next clock cycle.

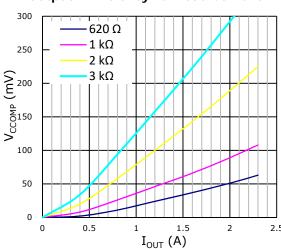

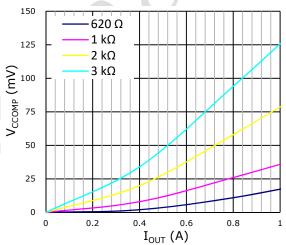

## Compensation for Output Cord Voltage Drop

In charger applications, the voltage drop across the output cord is significant in high current charging process. In some cases, excessive voltage drop across the output cord will even extend the charging time if high impedance output cord is used. The AP2963 integrated a cable compensation function. When the output current increases, the CC pin sinks current into the IC to increase the voltage drop across the resistor, RCC, in order to increase the output voltage. The sinking current of the CC pin is proportional to the voltage across CSP and CSN1 pins plus CSP and CSN2 pins. Thus, the cable compensation function can increase the output voltage according to the load. This increment of voltage at the node of inductor is called Cable Compensation Voltage (VCCOMP). The value of RCC determines the gain of the cable compensation. The value of RCC can be calculated using Equation 1.

$$R_{CC} = \frac{V_{CCOMP}}{(I_{OUT_1} \times R_{S_1} + I_{OUT_2} \times R_{S_2}) \times K}$$

(1)

### where

- R<sub>CC</sub> is the value of the resistor between CC pin and the node of the inductor.

- V<sub>CCOMP</sub> is the cable compensation voltage measured at the node of the inductor.

- I<sub>OUT1</sub> is the output current of channel 1.

- IOUT2 is the output current of channel 2.

- K is a constant which is ~ 1.4mA.

- R<sub>S1</sub> is the value of the sensing resistor of channel 1.

- R<sub>S2</sub> is the value of the sensing resistor of channel 2.

### CV / CC Mode Control

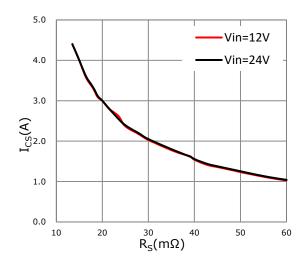

The AP2963 features a CV / CC function. It operates either in CV mode or CC mode. The CC limits for each channel can be programed through CSP, CSN1 and CSN2 pins individually. The CC mode provides an accurate current limiting function which is programed through the sensing resistors, RS1 and RS1. Output current can increase until it reaches the CC limit set by the sensing resistors. At this point, the AP2963 will transit from regulating output voltage to regulating output current, and the output voltage will drop with increasing load. The AP2963 can output up to 4A current and provide dual output with individual CC limits. Figure 2. shows the CC limit verse sensing resistor, RS1 or RS2. The CC limit should be set at a level which is slightly higher than the required output current. For example, 2.4A and 1.5A outputs are required for channel 1 and channel respectively. According to Figure 2. 25 m $\Omega$  and 50 m $\Omega$  sensing resistors should be selected for ensuring 2.4 A and 1.2 A continuous output currents.

Figure 2. CC Limit v.s. R<sub>S</sub>

In CV mode, the voltage at CC pin is regulated at 5 V. The output voltage in no load condition is 5 V. The output voltages of channel 1(VOUT1) and the output voltages of channel 2(VOUT2) can be calculated using Equation 2.

$$V_{OUT*} = 5V + V_{CCOMP} - (I_{OUT*} \times R_{S*})$$

(2)

### where

- $V_{\text{OUT}*}$  is the output voltage of channel 1 or channel 2.

- V<sub>CCOMP</sub> is the cable compensation voltage measured at the node of the inductor.

- R<sub>CC</sub> is the value of the resistor between CC pin and the node of the inductor.

- $I_{\text{OUT}^*}$  is the output current of channel 1or channel 2.

- R<sub>S\*</sub> is the value of the sensing resistor of channel 1 or channel 2.

### Cycle by Cycle Peak Current Limit

The peak current limit prevents the AP2963 from high inductor current and from drawing excessive current from the input voltage rail. Excessive current might occur with a shorted or saturated inductor or a heavy load or shorted output circuit condition. If the inductor current reaches the peak limit threshold, the high-side MOSFET is turned off and the low-side MOSFET is turned on to ramp down the inductor current.

### Input Under-voltage Lockout (UVLO)

An input UVLO circuit prevents the converter from starting the operation until the input voltage rises above the typical UVLO threshold of 4.5 V. A hysteresis of 500 mV is added so that the device cannot be disabled again until the input voltage drops below 4 V. This function implemented order in to malfunctioning of the device when the input voltage is between 4 V and 4.5 V.

### **CSP Over Voltage Protection (OVP)**

The CSP pin senses the output voltage at node between the sensing resistors, RS1 and RS2. If the voltage at CSP pin is detected above CSP OVP threshold of 5.8 V typically, the device stops switching immediately until the voltage at the CSP pin drops the hysteresis voltage lower

than CSP OVP threshold. This function prevents the device as well as the output capacitors from damage by high voltage on the output even though the feedback loop is faulty broken, i.e. R<sub>CC</sub> is open.

### Input Over Voltage Protection (OVP)

The input OVP is an additional function to protect the device from damage in a condition which is above the specified input voltage range. Once the input voltage is raising above input OVP threshold, 38 V typically, the AP2963 stops switching to reduce the chance of damage by the voltage spike at SW pin. The device goes back to normal operation until the input voltage falls a hysteresis about 1 V below the input OVP threshold.

#### Mode Output Under Hiccup Voltage Protection (UVP)

There is a CSP UVP threshold. If the threshold is hit, the hiccup mode output UVP will be triggered by disabling the converter and restarts soft-start after a predefined interval about 1 s. The AP2963 repeats this mode until the under voltage condition is removed. This function prevents the damage of the system from hardshort condition and the soft-short condition from the over current of portable device.

### Soft Start

The AP2963 implements the soft start function to reduce the inrush current during startup. The soft start begins once the input voltage raises above typical UVLO threshold of 4.5 V. The soft start time is typically 2 ms.

### Thermal Shutdown

A thermal shutdown is implemented to prevent the damage due to excessive heat and power dissipation. Typically, the thermal shutdown happens at the junction temperature of 165 °C. When the thermal shutdown is triggered, the device stops switching until the junction temperature drops the hysteresis temperature lower than thermal shutdown threshold, then the device starts switching again.

### **Application Information**

**Design Requirements**

| besign Requirements                |               |  |  |  |  |  |

|------------------------------------|---------------|--|--|--|--|--|

| Design Parameters                  | Target Values |  |  |  |  |  |

| Input Voltage Range                | 6 V to 40 V   |  |  |  |  |  |

| Typical Input Voltage              | 24 V          |  |  |  |  |  |

| Output Voltage                     | 5 V           |  |  |  |  |  |

| Channel 1 Output<br>Current Rating | 2.4 A         |  |  |  |  |  |

| Channel 1 Output<br>Current Rating | 1.0 A         |  |  |  |  |  |

| V <sub>CCOMP</sub> at Full Load    | 285 mV        |  |  |  |  |  |

**Table 1. Design Parameters**

### **Setting the CC Limit**

The typical application circuit is showed on the front page. Table 2 shows the CC limit verse sensing resistor. According to this figure,  $R_{\rm S1}$  and  $R_{\rm S2}$  should be set at 25 m $\Omega$  to output 2.4 A continuous current and 50 m $\Omega$  to output 1 A continuous current respectively.

## Setting the Cable Compensation Resistor(R<sub>CC</sub>)

The resistor,  $R_{CC}$ , solely determines the gain of the cable compensation. By subtitling  $V_{CCOMP}$ ,  $I_{OUT},\,R_S$  and K into the Equation 1,  $R_{CC}=2k\Omega.$  Table 2 and shows the cable compensation voltage at different load with  $R_{CC}=2k\Omega,\,R_{S1}=25~m\Omega$  and  $R_{S2}=50~m\Omega.$

| Total I <sub>LOAD</sub> (%) | Total I <sub>LOAD</sub> (A) | I <sub>LOAD1</sub> (A) | I <sub>LOAD2</sub> (A) | V <sub>CCOMP</sub> (mV) |  |

|-----------------------------|-----------------------------|------------------------|------------------------|-------------------------|--|

| 0                           | 0.00                        | 0.00                   | 0.00                   | 0.0                     |  |

| 10                          | 0.25                        | 0.24                   | 0.10                   | 28.4                    |  |

| 20                          | 0.50                        | 0.48 0.20              |                        | 56.8                    |  |

| 30                          | 0.75                        | 0.72                   | 0.30                   | 85.3                    |  |

| 40                          | 1.00                        | 0.96                   | 0.40                   | 113.7                   |  |

| 50                          | 1.25                        | 1.20                   | 0.50                   | 142.1                   |  |

| 60                          | 1.50                        | 1.44                   | 0.60                   | 170.5                   |  |

| 70                          | 1.75                        | 1.68                   | 0.70                   | 198.9                   |  |

| 80                          | 2.00                        | 1.92                   | 0.80                   | 227.4                   |  |

| 90                          | 2.25                        | 2.16                   | 0.90                   | 255.8                   |  |

| 100                         | 3.40                        | 2.40                   | 1.00                   | 284.2                   |  |

Table 2. Cable Compensation Voltage at Different Load

### Inductor Selection

Since the selection of the inductor affects the power supply's steady state operation, transient behavior, loop stability, and overall efficiency, the inductor is the most important component in switch power regulator design. Three most important specifications to the performance of the inductor are the inductor value, DC resistance, and saturation current.

The AP2963 designed to work with inductor values between 15  $\mu$ H to 47  $\mu$ H. A 15  $\mu$ H inductor is typically available in a smaller or lower-profile package, while a 47  $\mu$ H inductor produces lower inductor current ripple. If the output current is limited by the peak current limit of the IC, using a 47  $\mu$ H inductor can maximize the converter's output current capability.

The tolerance of inductors can be ranging from 10 % to 30 %. The inductance will further decrease 20 % to 35 % from the value of zero bias current depending on the definition of

saturation by inductor manufacturers. The basic requirements of selecting an inductor are the saturation current must be higher than the peak switching current and the DC rated current is higher than the average inductor current in normal operation. In buck converter, the average inductor current is equal to the total output current. The inductor value can be derived from the Equation 3.

$$L = \frac{(V_{OUT} + V_{CCOMP}) \times (V_{IN} - V_{OUT} - V_{CCOMP})}{V_{IN} \times \Delta I_L \times F_{SW}}$$

(3)

### where

- $\Delta I_L$  is the inductor peak-to-peak ripple current.

- V<sub>OUT</sub> = 5 V (output voltage at no load).

- V<sub>CCOMP</sub> is the cable compensation voltage measured at the node of the inductor.

- V<sub>IN</sub> is the input voltage.

- F<sub>SW</sub> is the switching frequenc

Lower inductor value results in higher ripple current and vice versa. Choose inductor ripple current approximately 30 % of the maximum load current, 4.2A, or  $\Delta I_L=1.02$  A. By subtitling  $V_{IN}(typ.),\ V_{OUT},\ V_{CCOMP},\ \Delta I_L$  and  $F_{SW}(typ.)$  into the above equation, the inductor value, L, is 33  $\mu H$ . The common inductor value is 33  $\mu H$ .

The saturation current of the inductor must be

higher than the maximum output current, 4A, plus half of the inductor ripple current in worst case, i.e. highest operating  $V_{IN}(38V)$ , lowest  $F_{SW}(105kH)$ , lowest inductor value(-10  $\sim$  -30% from nominal value), to prevent the core from saturation. Table 3 lists a typical toroid inductor that meet target applications for the design requirements.

| Core<br>Manufacturer         | Core Part<br>Number | L(µH)  | No. of<br>Turns | Wire Ø<br>(mm) | μ   | AL<br>(nH/N²) | Size[ODxIDxH]<br>(mm) |  |

|------------------------------|---------------------|--------|-----------------|----------------|-----|---------------|-----------------------|--|

| KDM Magnetic<br>Powder Cores | KS050-125A          | 33±10% | 24              | 0.8            | 125 | 56            | 12.7x7.62x4.75        |  |

Table 3. Recommended Toroid Inductor

### Input Capacitor Selection

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent high frequency switching current passing to the input. A low ESR input capacitor sized for maximum RMS current must be used. Multilayer Ceramic Capacitor(MLCC) with X5R or X7R dielectric is highly recommended because of their low ESR, low temperature coefficients and compact size characteristics. A 22  $\mu F$  MLCC is sufficient for most of

### applications.

### **Output Capacitor Selection**

The output capacitor is required to keep the output voltage ripple small and to ensure regulation loop stability. The output capacitor must have low impedance at the switching frequency. MLCC with X5R or X7R dielectric is recommended due to their low ESR and compact size characteristics. The output ripple,  $\Delta V_{OUT}$ , is determined by:

$$\Delta V_{\text{OUT}} \le \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{In}} \times F_{\text{SW}} \times L} \times \left( \text{ESR} + \frac{1}{8 \times F_{\text{SW}} \times C_{\text{OUT}}} \right)$$

(4)

### **Layout Considerations**

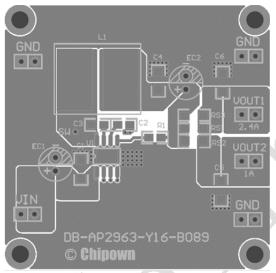

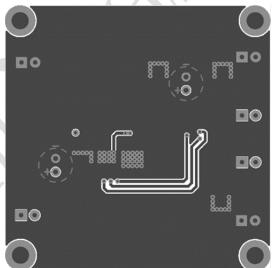

When doing the PCB layout, the following suggestions should be taken into consideration to ensure proper operation of the AP2963. These suggestions are also illustrated graphically in **Figure 3** and **Figure 4**.

- 1. The power path including the GND trace, the SW trace and the VIN trace should be as short as possible, direct and wide.

- 2. The cable compensation resistor must be connected to the center point of both sensing resistors directly.

- The input decoupling MLCC should be placed as close to the VIN and GND pins as possible and connected to input power plane and ground plane directly. This capacitor provides the AC current to the internal power MOSFET.

- 4. The power path between the output MLCC,

- C<sub>4</sub>, and the power inductor should be keep short and the other terminal of the capacitor should connect to the ground plane directly to reduce noise emission.

- 5. Keep the switching node, SW, away from the sensitive cable compensation path.

- Keep the negative terminals of input capacitor and output capacitor as close as possible.

- 7. Use Kelvin sense connection technique from the sensing resistors,  $R_{\text{S1}}$  and  $R_{\text{S2}}$ , pads directly to the CSP, CSN1 and CSN2 pins to achieve accurate CC limit.

- 8. Use large copper plane and thermal vias for GND for best heat dissipation and noise immunity.

Figure 3. Top Layer

Figure 4. Bottom Layer

### **Typical Performance Characteristics**

All curves taken at  $V_{IN} = 12V$  with configuration in typical application circuit shown in this datasheet.  $T_A =$ 25°C, unless otherwise specified.

**Output1 Efficiency vs. Load Current**

Figure 6. **Output2 Efficiency vs. Load Current**

Figure 7. Cable Compensation Voltage(V<sub>CCOMP</sub>) vs. Output1 Load Current

Figure 8. Cable Compensation Voltage(V<sub>CCOMP</sub>) vs. Output2 Load Current

# Chipown

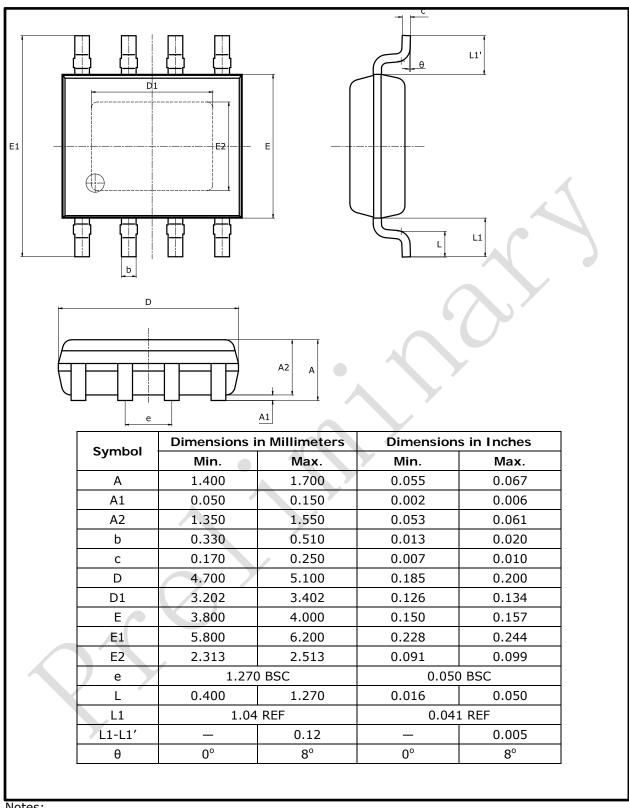

### Notes:

- 1. This drawing is subjected to change without notice.

- 2. Body dimensions do not include mold flash or protrusion.

- 3. This package conforms to JEDEC MS-012, variation BA.

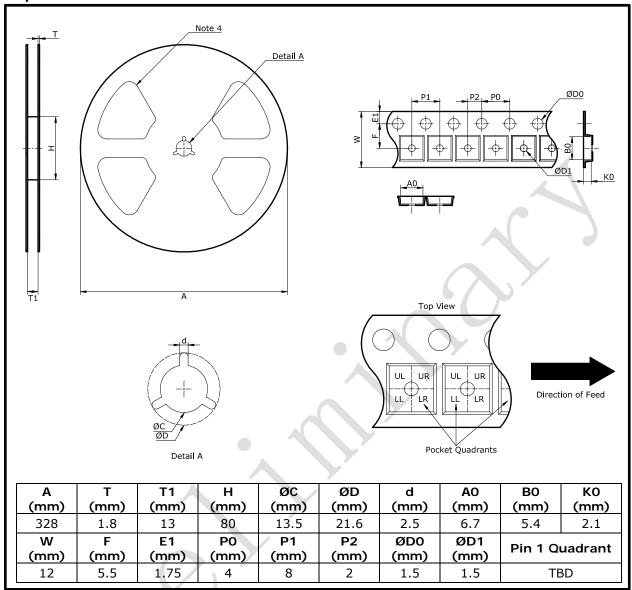

### **Tape and Reel Information**

### Notes:

- 1. This drawing is subjected to change without notice.

- 2. All dimensions are nominal and in mm.

- 3. This drawing is not in scale and for reference only. Customer can contact Chipown sales representative for further details.

- 4. The number of flange openings depends on the reel size and assembly site. This drawing shows an example only.

Rev. 0.2C