# SD691X 系统设计参考

杭州士兰微电子股份有限公司

地址: 杭州市黄姑山路 4号

邮编: 310012

主页: www.silan.com.cn

# 声明:

- ◆ 士兰保留本文档的更改权,恕不另行通知!

- 产品提升永无止境,我公司将竭诚为客户提供更优秀的产品!

# 目 录

| 1. | SD6912 | X 系列产  | :品简介                | 2  |

|----|--------|--------|---------------------|----|

|    | 1.1.   | 主要特    | 点                   | 2  |

|    | 1.2.   | SD691  | X 系列分类、管脚排列和管脚定义    | 2  |

|    | 1.2    | 2.1.   | SD691X 系列分类         | 2  |

|    | 1.2    | 2.2.   | SD6910A 管脚排列和管脚定义   | 2  |

|    | 1.2    | 2.3.   | SD691XS 管脚排列和管脚定义   |    |

|    | 1.2    | 2.4.   | SD691XD 管脚排列和管脚定义   | 4  |

| 2. |        |        | .用                  |    |

| 3. | 系统设i   | 计应用笔   | 记                   | 6  |

|    | 3.1.   | VCC 的  | 9设计                 | 6  |

|    | 3.2.   | FB 的词  | 设计                  | 6  |

|    | 3.3.   | Vcc 电  | 压、FB 分压网络以及辅助绕组匝比设置 | 7  |

|    | 3.3    | 3.1.   | R3、R4 设置            |    |

|    | 3.3    | 3.2.   | 匝比设置                | 7  |

|    | 3.3    | 3.3.   | VCC 电压              | 7  |

|    | 3.4.   | COMP   | 的设计                 | 7  |

|    | 3.5.   | SOUR   | CE 的设计              | 8  |

|    | 3.6.   | GND fi | 勺设计                 | 8  |

|    | 3.7.   | 电感的    | 设计                  | 8  |

|    | 3.8.   | PCB 有  | 5版及 EMI 常规注意事项      | 9  |

|    | 3.9.   | 环境湿    | 度及抗干扰的注意事项          | 9  |

|    | 3.10.  | 系统调    | 试常见问题小结             | 10 |

|    | 3.     | 10.1.  | 提高 PF 值方法           | 10 |

|    | 3.1    | 10.2.  | 连续关开机电流过冲及低压启动调试    | 10 |

|    | 3.11.  | 其它设    | 计注意事项               | 11 |

# 1. SD691X 系列产品简介

#### 1.1. 主要特点

- ◆ 非隔离升降压式电路结构(BUCK-BOOST)

- ◆ 临界导通模式

- ◆ 超低 IC 启动电流,系统快速启动

- ◆ 前沿消隐和固定导通时间控制

- ◆ VCC 过压保护、VCC 欠压锁定以及过温保护

- ◆ 逐周期限流

- ◆ 峰值电流补偿

- ◆ LED 短路保护和 LED 开路保护

#### 1.2. SD691X 系列分类、管脚排列和管脚定义

#### 1.2.1. SD691X 系列分类

| IC 名称   | 封装形式           | MOS | 导通电阻 R <sub>DS(ON)</sub> | 漏源击穿电压 BV <sub>DSS</sub> |

|---------|----------------|-----|--------------------------|--------------------------|

| SD6910A | SOP-8-225-1.27 | 外置  | Y                        | 1                        |

| SD6911S | SOP-7-225-1.27 | 内置  | 13Ω                      | >650V                    |

| SD6912S | SOP-7-225-1.27 | 内置  | 4.4Ω                     | >650V                    |

| SD6914S | SOP-7-225-1.27 | 内置  | 1.95Ω                    | >650V                    |

| SD6914D | DIP-7-300-2.54 | 内置  | 2.3Ω                     | >650V                    |

| SD6917D | DIP-7-300-2.54 | 内置  | 1.1Ω                     | >650V                    |

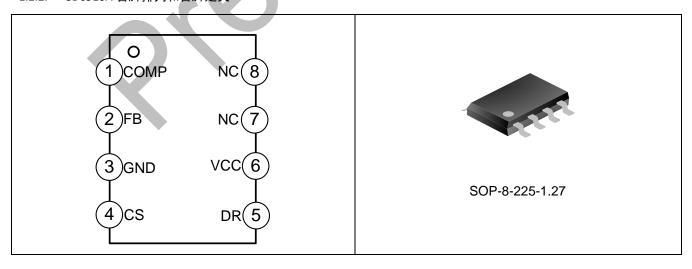

#### 1.2.2. SD6910A 管脚排列和管脚定义

图 1: SD6910A 管脚排列图和封装示意图

|      | ı    | ı   | 衣 1: SD091A 自脚足入   |

|------|------|-----|--------------------|

| 管脚号  | 管脚名称 | 1/0 | 功 能 描 述            |

| 1    | COMP | I/O | 用 RC 环路补偿,跨导放大器输出端 |

| 2    | FB   | I   | 反馈电压检测脚            |

| 3    | GND  | I/O | 地                  |

| 4    | CS   | I   | 电流采样脚              |

| 5    | DR   | 0   | 栅驱动脚               |

| 6    | VCC  | I/O | 芯片供电脚              |

| 7, 8 | NC   | -   | 空脚                 |

表 1: SD691X 管脚定义

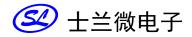

# 1.2.3. SD691XS 管脚排列和管脚定义

图 2: SD691XS 管脚排列图和封装示意图

| 表 2: SD691X 管脚定 |

|-----------------|

|-----------------|

| 管脚号  | 管脚名称   | 1/0 | 功能描述                  |

|------|--------|-----|-----------------------|

| 1    | FB     |     | 反馈电压检测脚               |

| 2    | COMP   | 1/0 | 用 RC 环路补偿,跨导放大器输出端    |

| 3    | VCC    | I/O | 芯片供电脚                 |

| 4    | SOURCE | I/O | MOSFET 的源极和控制芯片的电流采样脚 |

| 5, 6 | DRAIN  | I/O | MOSFET 的漏极            |

| 7    | GND    | I/O | 地脚                    |

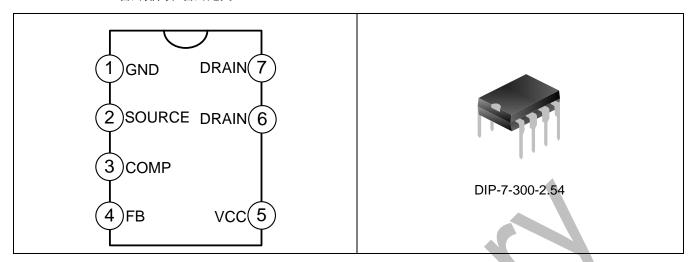

#### 1.2.4. SD691XD 管脚排列和管脚定义

图 3: SD691XD 管脚排列图和封装示意图

表 3: SD691XD 管脚定义

| 管脚号  | 管脚名称   | 1/0 | 功 能 描 述              |

|------|--------|-----|----------------------|

| 1    | GND    | I/O | 地                    |

| 2    | SOURCE | I/O | MOSFET的源极和控制芯片的电流采样脚 |

| 3    | COMP   | I/O | 用 RC 环路补偿,跨导放大器输出端   |

| 4    | FB     | 1   | 反馈电压检测脚              |

| 5    | VCC    | I/O | 芯片供电脚                |

| 6, 7 | DRAIN  | I/O | MOSFET 的漏极           |

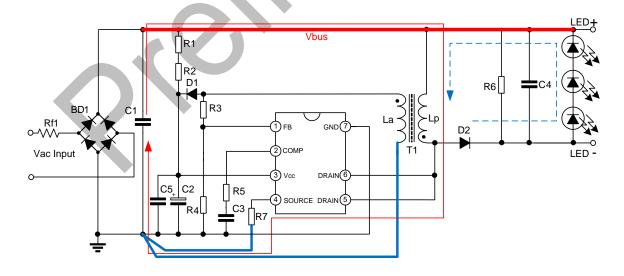

# 2. SD691X 典型应用

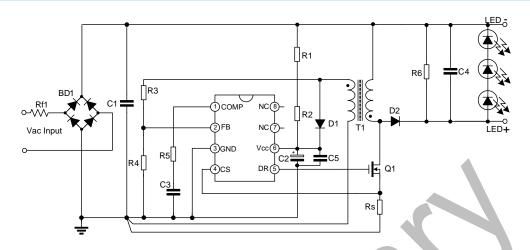

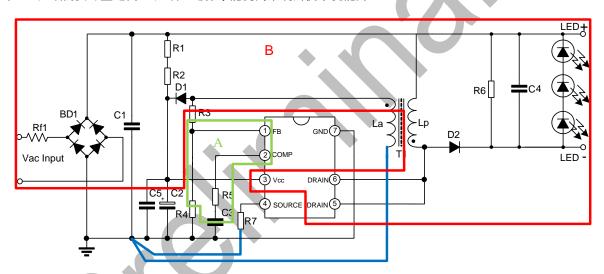

图 4: SD6910A 典型应用原理图

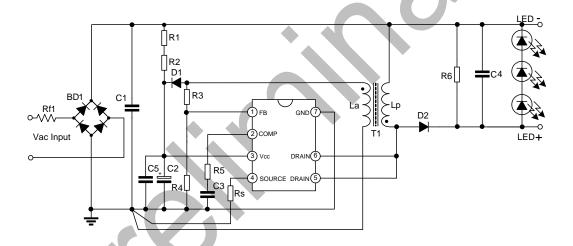

图 5: SD691XS 典型应用原理图

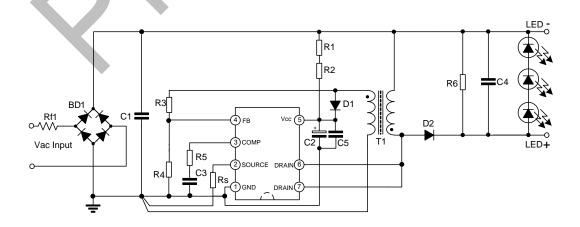

图 6: SD691XD 典型应用原理图

## 3. 系统设计应用笔记

#### 3.1. VCC 的设计

VCC 脚是给 IC 供电脚,在设计时要注意以下几点:

- 1. R1、R2 为启动之前给 C2\C5 充电的电阻,取值越小,启动时间越短;一般取 200K 到 600K (每颗),取值过小会影响系统效率。

- 2. C2 为 VCC 电容,它起到滤波和储能两个作用。一般取 4.7uF~22uF 电解电容,取值越大,启动时间越长;取 值不能过小,否则启动易发生 UVLO。 LAY 板时注意尽量靠近 IC 放置,同时建议并联陶瓷 C5 防止高频干扰。

- 3. 当 VCC 达到 15.9V 时,系统开始工作; 当 VCC 下降到 7.8V 时,系统停止工作。VCC 过压保护点为 26.5V(注意 VCC 电压纹波)。正常工作时,建议把 VCC 电压设定在 18V 左右。

- 4. VCC 辅助绕组供电回路中,建议增加一颗电阻,可以减小辅助源二极管正向峰值电流,同时可以防止由开关 噪声引起的 VCC 过高。

- 5. VCC 供电回路设计不合理,可能会导致系统无法正常工作。

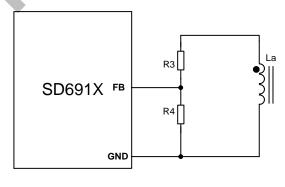

#### 3.2. FB 的设计

- 1. FB 脚为"零电流开通检测"输入端,典型应用电路如下图所示。当此脚电位低于内部基准 Vref 时,开通 MOS 管,使系统工作在临界连续模式。

- 2. FB 脚也为峰值电流补偿输入脚,通过调节 R3 的大小来改变补偿量。R3 减小,补偿量增加;反之,R3 增大,补偿量会减小。调节 R3 电阻可以将输入电压线性调整率调好。

- 3. LED 开路保护: 反激变压器的辅助绕组可以反射输出电压,当输出 LED 开路时,输出电压会不断上升,则 FB 脚电压也会相应上升,当 FB 电压高于内部基准时 (1.46V),就会进入 FB 过压保护,则认定为输出处于开路 状态并保护,且可以自动恢复。

- 4. LED 短路保护: 反激变压器辅助绕组可以反射输出电压,当输出 LED 短路时,FB 脚会出现低压状态,当 FB 电压低于内部基准 0.2V 且超出内部设定时间,IC 就会认为输出处于短路状态。关闭系统,等待 VCC 重启。

- 5. 在 LAY 板时, R3、R4 要靠近 FB 脚放置。要远离高压母线以及 MOS 管的漏极区域。

图 7: FB 外围电路

#### 3.3. Vcc 电压、FB 分压网络以及辅助绕组匝比设置

对于"典型应用"的系统,下面介绍了一些关键参数的设计过程,其中包括: FB 分压网络(R3、R4)、辅助绕组与主电感匝比(n2/n1)以及最终 Vcc 电压确定。

#### 已知参数:

最大输出电压: Vo (根据实际 LED 灯串确定)

空载输出电压: Vo1, 并且 Vo1≥Vo +8V (要确保公式成立)

辅助绕组电压: Va (指空载时电压,一般建议取值为 20V)

FB 过压基准: V<sub>FB OVP</sub> (内部设置为 1.46V)

#### 3.3.1. R3、R4 设置

$$\frac{R_3 + R_4}{R_4} = \frac{V_a}{V_{FB OVP}} \tag{1}$$

$$R_3 = \left(\frac{V_a}{V_{FB \text{ OVP}}} - 1\right) \times R_4 \tag{2}$$

假设 R4=20K,

$$R_3 = (\frac{20}{1.46} - 1) \times 20K \approx 254K \tag{3}$$

#### 3.3.2. 匝比设置

$$n = \frac{n2}{n1} = \frac{V_{01}}{V_a} \tag{4}$$

假设 Vo=80V、Vo1=Vo+8V,

$$n = \frac{80V + 8V}{20V} = 4.4 \tag{5}$$

#### 3.3.3. VCC 电压

$$V_{cc} = \frac{V_o}{n} = \frac{80V}{4.4} \approx 18.2V$$

(6)

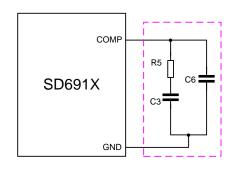

#### 3.4. COMP 的设计

- 1. COMP 脚为内部跨导放大器输出端,外接 RC 作补偿。建议在 LAY 板时,在空间许可的前提下,采用下图所示电路结构,可以消除由于 LAY 板不合理带来的高频噪声影响。

- 2. 电容 C3 取值, 一般建议在 1uF~2.2uF 之间; 电容 C6 取值, 一般建议在 1nF~10nF 之间; 电阻 R5 取值, 一

般建议在 0~1K 之间。

3. 所有补偿电路元件都要靠近 IC 的 COMP 脚和 GND 放置,不可距离太远,否则有可能会造成系统不稳定等现象。

图 8: COMP 外围电路

#### 3.5. SOURCE 的设计

SOURCE 为功率管电流采样输入脚,用于控制输出 LED 电流,典型输出电流计算公式,参考下面:

$$I_0 = \frac{1}{2} \times \frac{0.1}{R_s} \tag{7}$$

若输出电流值已经确定,同样可以根据公式求出需要的采样电阻值 Rs。

#### 3.6. GND 的设计

GND 为芯片接地脚,与辅助绕组以及主功率回路地线建议分开接地,避免造成干扰的可能。地线与高压线以及 MOS 管的漏极要保持一定的距离。

### 3.7. 电感的设计

输出滤波电感的设计,请参考下面简单设计流程:

已知条件:

输入电压范围: Vac\_min, Vac\_max

额定输出电压: Vo

输出电流: lo

效率:η

预先设定最低开关频率 fs\_min, 计算相应的导通时间 Ton:

$$T_{on} = \frac{V_O + V_F}{\left(\sqrt{2}V_{ac \min} + V_O + V_F\right) \times f_{s \min}}$$

(8)

计算电感量 L:

$$L = \frac{\left(V_{ac\_min} \times T_{on}\right)^2 \times \eta \times f_{s\_min}}{2 \times P_O}$$

(9)

根据磁芯有效面积(Ae)以及最大磁通密度 Bmax 可以确定原边绕组线圈匝数:

$$N_{P} = \frac{\sqrt{2} \times V_{in\_min} \times T_{on}}{Ae \times B_{max}}$$

(10)

辅助供电绕组设计:

$$N_{a} = \frac{V_{CC} \times N_{P}}{V_{O}}$$

(11)

VCC 取值请参考规格书,一般建议在 18V 左右。

#### 3.8. PCB 布版及 EMI 常规注意事项

- 1. CS 采样电阻要靠近 IC 采样脚,同时采样路径要尽可能的短。

- 2. 芯片 COMP 脚附件或下面尽量不要走高频高压线。

- 3. MOS 管漏极与整流二极管阳极连接端面积要小。

- 4. 主功率回路(Loop1&Loop2)路径要尽可能短,LAY 板时,可以将整流桥后电容(C1)靠近变压器、MOS管及二极管侧放置。

- 5. 采样电阻接地端以及辅助绕组接地端需要跟 IC 其余外围器件接地端分开走线。

图 9: GND 走线以及主功率回路示意图(以 SD691XS 为例)

#### 3.9. 环境湿度及抗干扰的注意事项

系统的设计需要考虑外界不良因素对系统正常工作的影响。目前对系统影响最显著的就是环境湿度。

高湿环境下,各个焊盘及引线之间可能会存在"通路",此"通路"一般由水、或助焊剂、或其余异常因素组成。此通路的阻抗较大,对IC 大多数管脚不会有大的影响。但是对一些高阻的管脚以及高灵敏性的管脚会有明显的影响。

以 SD691XS 系列为例,易受影响的管脚如下:

#### 1. COMP

COMP 呈现高阻态,所以其比较容易接收到外界的异常信号。高湿环境下,PCB 上裸露的焊盘(靠近 COMP 脚的)和走线与 COMP 之间就可能存在异常"通路"。如果这些焊盘相对于 COMP 的电压差异较大或者本身有很强的干扰信号,那么就会引起 COMP 的异常,最终导致系统工作异常。

#### 2. FB

FB 采样的信号关系到系统的过压保护、过零检测以及短路保护。因此保证其信号的洁净,对系统稳定工作非常重要。异常"通路"会引进异常干扰信号。从而引起系统过压点下降等问题,也就是引起 LED 灯闪或者无法启动。

下图中 A 区域是连接 FB 和 COMP 的走线以及焊盘。B 区域是高电压以及存在较大干扰信号的走线和焊盘。在 PCB 布局时,B 区域需要尽量远离 A 区域。这样才能提高系统的抗干扰能力。

图 10: 高压区域和易受干扰区域示意图(以 SD691XS 为例)

#### 3.10. 系统调试常见问题小结

#### 3.10.1. 提高 PF 值方法

- 1. 减小 AC 输入总容值,包括整流桥前面的差模电容(CX1)和后面的滤波电容(C1),在输出功率固定前提下,容值总和越大,系统 PF 值就越低,总和越小, PF 越高,但过小,低压输入会不稳定。

- 2. 补偿网络,包括 C3、C6 和 R5,C6 在多数系统中可以省去,而且它也不会影响 PF 值;C3 取值越大,PF 越高;R5 取值越小,PF 越高。过大的 C3,可能会引起低压启动困难。

#### 3.10.2. 连续关开机电流过冲及低压启动调试

1. 如果输入 AC 做连续快速的关开机动作,输出 LED 电流可能出现过冲,调试办法如下:

增大 R6 阻值,直到 LED 电流没有过冲。

2. R6 增大后,同时可能会造成低压输入时,比如 90VAC,开机存在二次或多次启动。在低压启动和高压过冲问题上,可以通过寻求合适的 R6 电阻值,最终保证没有过冲,也可以一次启动(同时可以增大 VCC 电容)。

#### 3.11. 其它设计注意事项

- 1. 输出滤波电容在选用时,除了考虑耐压之外,还要考虑输出电流的纹波要求;若要求输出电流纹波小,则需要的电容值就大。根据不同的应用需求来确定。同时建议用 ESR 较小的电容,以提高系统效率。

- 2. 由于有源功率因数校正控制,输入电容容量较小。一般选取 68nF~220nF 之间(根据输出功率确定,输出功率增大,容值相应增大)。

- 3. 输出电感的辅助绕组尽可能与主电感耦合好。

- 4. 输出端需要并联一颗较大电阻,以防止空载电压过高,比如 100K~200K。

- 5. IC 内部有限制最高频率功能,在某些系统中,由于效率,电感发热等因素的限制,输入高压的情况下,系统开 关频率被限制,系统就会出现断续现象,属于正常现象,不影响整机性能。

- 6. 建议用±1%精度的采样电阻,并用多颗并联。采样电阻不要使用直插功率电阻或金属膜电阻,最好使用表贴 电阻。

- 7. 不管在任何工作条件下,要保证系统器件的应力都没有超标,且品质可靠。

杭州士兰微电子股份有限公司 http://www.silan.com.cn

# 全世界销售机构联系方式

# 中国

#### 中国 浙江杭州市黄姑山路 4号

电话: 0571-88210880 传真: 0571-88212533

EMAIL: wangzengyao@silan.com.cn

#### 中国 深圳 福田区天安数码城时代大厦 A 座 2003 室

电话: 0755-83476269 传真: 0755-83476058

EMAIL: zhangwei@silan.com.cn

#### 台湾 台北市内湖区行善路 56 号 5 楼

电话: 02-8791-2482 传真: 02-8791-4431

EMAIL: lorettahuang@silan.com.tw

#### 韩国

# 京畿道,Anshan-City, Sangrok-Gu, Il-dong, Anshan-1 College, Venture B/D, Room #311

邮编: 426701

电话: +82-31-409-6858 / +82-70-8671-7415

传真: +82-31-409-6857 H/P:+86-18668157153 EMAIL: yeqiliu@silan.com.cn

| 产品 | 名称:  | SD691X        | 文档类型: | 系统证   | 设计参   | É              |  |

|----|------|---------------|-------|-------|-------|----------------|--|

| 版  | 权:   | 杭州士兰微电子股份有限公司 | 公司主页: | http: | //ww\ | w.silan.com.cn |  |

|    |      |               |       |       |       |                |  |

| 版  | 本:   | 0.1           |       | 作     | 者:    | 林星宇            |  |

| 修改 | 记录:  |               |       |       |       |                |  |

| ]  | . 初稿 |               |       |       |       |                |  |