# **Synchronous Rectification Driver**

# with Green Mode Function

### REV. 00

## **General Description**

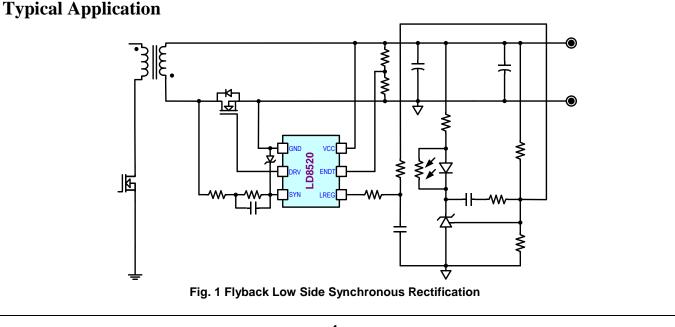

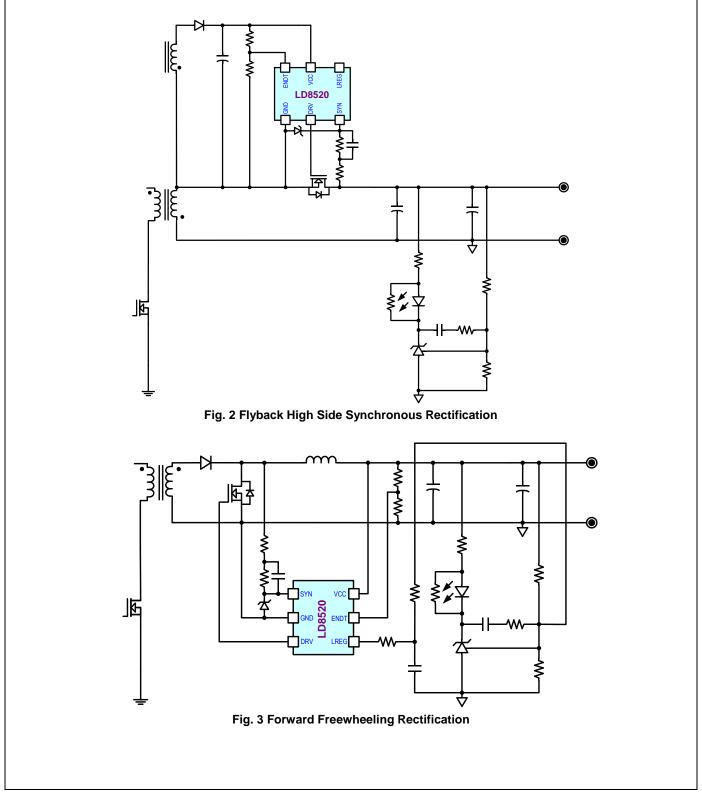

LD8520 is a secondary side Synchronous Rectification (SR) driver IC. With LD8520 Optimal Dead Time control method, switch power supply not only can achieve high efficiency in dynamic load but also operation safety.

LD8520 is suited for Flyback low side and high side Synchronous Rectification in CCM and DCM. For Forward Freewheeling Rectification application, LD8520 can be applied in CCM and DCM operation.

In light load condition, LD8520 will enter Green Mode to reduce operation current by stopping SR MOSFET driving function.

Load Regulation Improve function is an innovative design in LD8520. With this unique function, switch power supply can achieve better Load Regulation easily.

### Features

- Suited for Low Side and High Side Flyback

- Synchronous Rectification in CCM, DCM Suited for Forward Freewheeling Rectification in CCM and DCM.

- Optimal Dead Time Control

- Quickly Response for Dynamic Load

- Enable Function

- 250uA Ultra Low Green Mode Operation Current

- Load Regulation Improve Function

## Applications

- Switching AC/DC Adaptor and Battery Charger

- Open Frame Switching Power Supply

01/28/2015

LD8520 01/28/2015

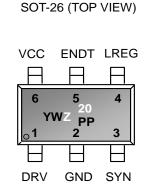

## **Pin Configuration**

YY, Y : Year code (D: 2004, E: 2005.....) WW, W : Week code PP, P : Production code Z20 : LD8520

# **Ordering Information**

| Part number | Package | TOP MARK | Shipping           |

|-------------|---------|----------|--------------------|

| LD8520GL    | SOT-26  | YWP/20   | 3000 /tape & reel  |

| LD8520GS    | SOP-8   | LD8520   | 3600 /tube /Carton |

The LD8520 is ROHS compliant/Green packaged.

## **Pin Descriptions**

| SOT-26 | SOP-8 | NAME | FUNCTION                                                                              |

|--------|-------|------|---------------------------------------------------------------------------------------|

| 1      | 3     | DRV  | Driving pin, connector to GATE pin of MOSFET directly or through a resistor           |

| 2      | 2     | GND  | Ground pin                                                                            |

| 3      | 1     | SYN  | The SYN pin is used to detect $V_{\text{DS}}$ of SR MOSFET through a voltage divider. |

| 4      | 8     | LREG | Load regulation compensation pin                                                      |

| 5      | 7     | ENDT | Enable & dead time setting pin,                                                       |

| 6      | 6     | VCC  | Supply voltage pin                                                                    |

|        | 4     | NC   | No connect                                                                            |

|        | 5     | NC   | No connect                                                                            |

**Absolute Maximum Ratings**

| VCC                                                       | -0.3V ~ 30V      |

|-----------------------------------------------------------|------------------|

| DRV                                                       | -0.3V ~ VCC+0.3V |

| SYN, ENDT, LREG                                           | -0.3V ~ 6V       |

| VCC pin Operating Current                                 | 50mA             |

| SYN pin Clamp Current                                     | 1mA / -1mA       |

| DRV pin Output Current                                    | 1A / -1.5A       |

| LREG pin Sink Current                                     | 0.5mA            |

| Operating Junction Temperature                            | -40°C ~ 125°C    |

| Storage Temperature Range                                 | -65°C ~ 150°C    |

| Package Thermal Resistance (SOT-26, $\theta_{JA}$ ).      | 200°C/W          |

| Package Thermal Resistance (SOP-8, $\theta_{JA}$ )        | 160°C/W          |

| Power Dissipation (SOT-26, at Ambient Temperature = 85°C) | 200mW            |

| Power Dissipation (SOP-8, at Ambient Temperature = 85°C)  | 250mW            |

| Lead temperature (Soldering, 10sec)                       | 260°C            |

| ESD Voltage Protection, Human Body Model                  | 2.5 KV           |

| ESD Voltage Protection, Machine Model                     | 250 V            |

|                                                           |                  |

### Caution:

Stresses beyond the ratings specified in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Recommended Operating Conditions**

| ltem                       | Min. | Max. | Unit |

|----------------------------|------|------|------|

| Supply Voltage VCC         | 9    | 28   | V    |

| SYN pin External Resistor  | 100K | 500K | Ω    |

| SYN pin External Capacitor | 10   | 150  | pF   |

| ENDT pin                   | 0    | 4.5  | V    |

| LREG pin External Resistor | 10K  | 10M  | Ω    |

## **Electrical Characteristics**

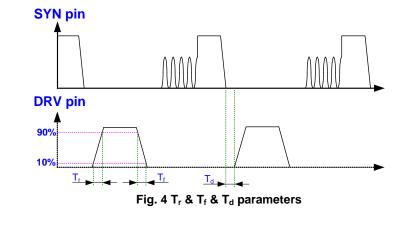

$(T_A = +25^{\circ}C \text{ unless otherwise stated}, VCC=12V)$

| PARAMETER                              | CONDITIONS                                | SYMBOL               | MIN  | ТҮР  | MAX  | UNITS |  |

|----------------------------------------|-------------------------------------------|----------------------|------|------|------|-------|--|

| Supply Voltage (VCC Pin)               |                                           |                      |      |      |      |       |  |

| UVLO(ON)                               |                                           | V <sub>CC_ON</sub>   | 7.5  | 8    | 8.5  | V     |  |

| UVLO Hysteresis                        |                                           | V <sub>CC_HYS</sub>  | 0.35 | 0.5  | 0.65 | V     |  |

| Operating Current                      | VCC=15V, SYN=65kHz,<br>1nF on DRV pin     | I <sub>VCC_OP</sub>  | 2    | 3    | 4    | mA    |  |

|                                        | Green Mode, SYN pin=4V                    | I <sub>VCC_GM</sub>  | 100  | 200  | 250  | uA    |  |

| SYN Reference (SYN Pin)                |                                           |                      |      |      |      |       |  |

| SYN High Threshold                     |                                           | V <sub>SYN_H</sub>   | 2.3  | 2.5  | 2.7  | V     |  |

| SYN Threshold Hysteresis               | Within 80ns at falling edge               | V <sub>SYN_HYS</sub> | 1.7  | 2    | 2.3  | V     |  |

| De-bounce time<br>after SYN pin=Low    | *                                         | T <sub>SYN_DBC</sub> | 100  | 300  | 500  | ns    |  |

| Clamp Voltage                          | SYN pin Input Current=1mA                 | $V_{SYN\_CLP}$       | 3.5  | 4    | 4.5  | V     |  |

| Max Input Current                      | *                                         | I <sub>SYN_MAX</sub> |      |      | 1    | mA    |  |

|                                        |                                           |                      |      |      | -1   | mA    |  |

| SYN Impedance                          | *                                         | Z <sub>SYN</sub>     | 1    |      |      | MΩ    |  |

| Output Driver (DRV Pin)                |                                           |                      |      |      |      |       |  |

| Output High Voltage                    | VCC=12V, Io=10mA                          | V <sub>DRV_H</sub>   | 9    |      |      | V     |  |

| Output Low Voltage                     | VCC=12V, Io=-10mA                         | V <sub>DRV_L</sub>   |      |      | 0.5  | V     |  |

| Output Clamp Voltage                   | VCC=19V                                   | V <sub>DRV_CLP</sub> | 11   | 13   | 15   | V     |  |

| Source Capability                      | *, VCC=12V, Load Capacitor=33nF           | I <sub>DRV_SOC</sub> |      | 1    |      | А     |  |

| Sink Capability                        | *, VCC=12V, Load Capacitor=33nF           | I <sub>DRV_SNK</sub> |      | -1.5 |      | А     |  |

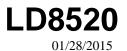

| Rising Time                            | VCC=12V, Load Capacitor=1nF<br>GATE=2V~9V | Tr                   |      | 150  |      | ns    |  |

| Falling Time                           | VCC=12V, Load Capacitor=1nF<br>GATE=9V~2V | T <sub>f</sub>       |      | 30   |      | ns    |  |

| Propagation Delay Time<br>to GATE High | VCC=12V, T <sub>r</sub> : 0%~10%          | T <sub>d</sub>       | 20   | 100  | 200  | ns    |  |

| Max on time                            |                                           | T <sub>DRV_MAX</sub> | 15   | 25   | 35   | us    |  |

01/28/2015

LD8520

01/28/2015

| PARAMETER                                    | CONDITIONS                                       | SYMBOL                | MIN | TYP | MAX | UNITS   |  |

|----------------------------------------------|--------------------------------------------------|-----------------------|-----|-----|-----|---------|--|

| Enable Function (ENDT Pin)                   |                                                  |                       |     |     |     |         |  |

| Enable Voltage                               |                                                  | V <sub>EN</sub>       | 1.9 | 2   | 2.1 | V       |  |

| ENDT pin OVP                                 |                                                  | V <sub>EN_OVP</sub>   | 5   | 5.5 | 6   | V       |  |

| ENDT pin OVP                                 | *                                                | Ŧ                     | 00  | 50  | 400 |         |  |

| de-bounce time                               | ^                                                | T <sub>EN_OVDBC</sub> | 20  | 50  | 100 | us      |  |

| Min. Dead Time Setting (ENDT Pin)            |                                                  |                       |     |     |     |         |  |

| Detecting Current                            | EN pin= V <sub>EN</sub>                          | I <sub>DT_DET</sub>   | 9   | 10  | 11  | uA      |  |

|                                              | Dead Time A                                      |                       | 0.7 | 1.0 | 1.3 | us      |  |

|                                              | External Resistor < 60kΩ                         |                       |     |     |     |         |  |

| Minimum Dead Time                            | Dead Time B                                      | Тат                   | 1.2 | 1.5 | 1.8 | us      |  |

| Setting                                      | External Resistor =100k $\Omega$ ~ 130k $\Omega$ | I DT                  |     |     |     |         |  |

|                                              | Dead Time C                                      |                       | 1.7 | 2.0 | 2.3 | us      |  |

|                                              | External Resistor > 200kΩ                        |                       |     |     |     |         |  |

| Load regulation Compensation (LREG Pin)      |                                                  |                       |     |     |     |         |  |

| Input Impedance                              | *                                                | 7                     |     |     | 50  | Ω       |  |

| when switch close                            |                                                  | Z <sub>LRG_CLS</sub>  |     |     | 50  | 22      |  |

| Input Impedance                              | *                                                | 7                     | 1   |     |     | MΩ      |  |

| when switch open                             |                                                  | Z <sub>LRG_OPN</sub>  | I   |     |     | 111 2 2 |  |

| On Chip OTP (Over Temperature) Auto-Recovery |                                                  |                       |     |     |     |         |  |

| OTP Level                                    | *                                                | T <sub>OTP</sub>      |     | 140 |     | °C      |  |

| OTP Hysteresis                               | *                                                | T <sub>OTP_HYS</sub>  |     | 30  |     | °C      |  |

\*: Guaranteed by designed.

## **Application Information**

#### **Operation Overview**

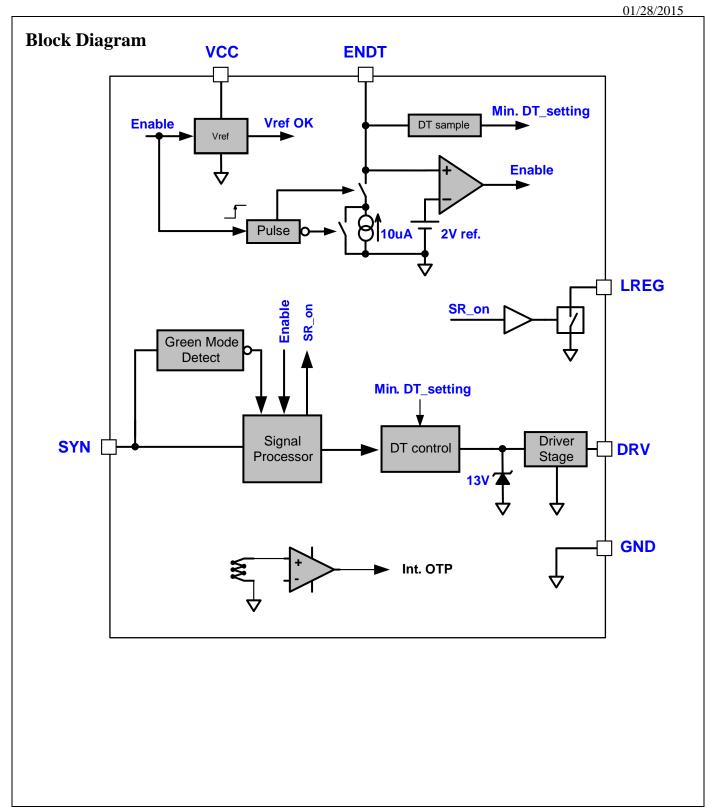

LD8520 is a secondary side Synchronous Rectification driver IC for CCM and DCM operation. LD8520 not only has excellent dead time control function for safety in load transient, but also only needs very few operation current in green mode. In addition, LREG pin provides a possibility to improve load regulation; it is useful for power supply with high output current.

# Under Voltage Lockout (UVLO) and Enable Function

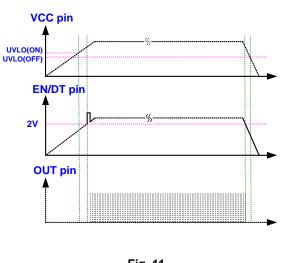

The UVLO(ON) and UVLO(OFF) are 8.0V and 7.5V, respective. Besides VCC pin > UVLO(ON), ENDT pin > 2V is necessary to achieve DRV pin output signal.

In general design, the recommend sequence shown as Fig. 11

Turn-on sequence: VCC > UVLO(ON)  $\rightarrow$  ENDT > 2V  $\rightarrow$  DRV enable

Turn-off sequence:

ENDT < 2V  $\rightarrow$  DRV disable  $\rightarrow$  VCC < UVLO(OFF)

With enable function, Synchronous Rectifier always operates in stable condition. Therefore, some unstable transient like turn-on, turn-off, SURGE, ESD...etc. would not make Synchronous Rectifier working unsafe.

LD8520

01/28/2015

#### Fig. 11

### **Dead Time Setting**

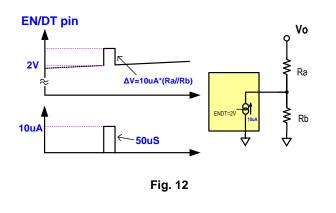

Besides enables function, ENDT pin has minimum dead time setting function also. When ENDT pin=2V, ENDT pin will source 10uA to detect its external resistance for 50us, as shown in Fig. 12 At that moment, ENDT pin voltage can be described as [10uA \* (Ra//Rb)+2V], higher voltage level means longer minimum dead time. The detection function works one time only after VCC pin > UVLO(ON), and the setting would be memorized until VCC < UVLO(OFF).

#### **SYN Pin Behavior**

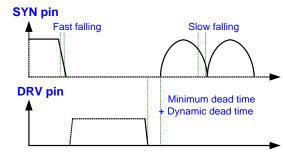

SYN pin detect system behavior, then the internal logic circuit determine when DRV pin turn-on and turn-off, what dynamic dead time is at system in load transient, when LD8520 enter/leave green mode.

As shown in Fig.13, when SYN pin voltage falling fast, that means secondary-side current goes through SR MOSFET and LD8520 will drive DRV pin immediately. Otherwise, falling slow signal on SYN pin would be judged as DCM ring on primary-side, that would not trigger DRV pin high. When system operates in steady condition, the real dead time would close to minimum dead time. In some case of load transient, line voltage change, output short, output over voltage...etc., variable SYN pin signal would causes increasing dynamic dead time to make sure system safety.

When system operates in burst mode, LD8520 works in green mode also. That means LD8520 only needs less than 250uA operation current by its advanced circuitry.

Fig. 13

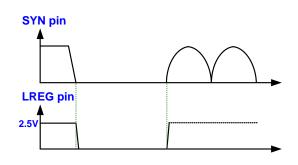

#### LREG Pin Behavior

In some higher output current system, series voltage drop on output cable would cause worse load regulation. There is a signal level switch inside LREG pin, the switch turn on by SYN signal. Generally, LREG internal switch has low impedance when secondary-side current existence, as shown in Fig. 14.

LD8520

01/28/2015

Fig. 14