BM1050AF-G

#### General Description

BM1050AF is compounded LSI of Power Factor Correction converter (PFC) for harmonic solution and DC/DC converter (DC/DC). Because DC/DC operates on Quasi-resonant method, DC/DC contributes to Low EMI.

BM1050AF built in a HV starter circuit that tolerates 650V. Because of putting the current sense resistors externally both the PFC part and the DC/DC part, IC enables power supply design free.

In the PFC part, IC adopts peak current control operation. Suitable application is proposed by a various protection circuit, such as the multiplier with a revision circuit on the AC voltage falls, the load regulation revision circuit, and the maximum power feed-forward circuit, etc.

Moreover, the frequency hopping function is built in and it contributes to low EMI.

The Quasi-resonant system of a DC/DC part contributes to low EMI because PFC operates by soft switching. A burst mode is built in, so the power is reduced at light load. Various protection functions, such as a soft start function, a burst function, an over-current limiting for every cycle, overvoltage protection, and over current protection, are built in. The pin for communicated control with a controller and the external stop pin are prepared; it proposes the system that can be adapted for various applications.

## Basic specifications

• Operating Power Supply Voltage Range:

VCC : 8.5 to 24.0V

- Operating Current:

- QR ON (PFC OFF) : 1.20mA(pulse on) QR ON (PFC OFF) : 1.00mA(pulse off) QR ON (PFC ON) : 1.80mA(pulse on)

- Oscillation Frequency QR part :120kHz(FB=2.0V typ)

- Operating Temperature: -40°C to +85°C

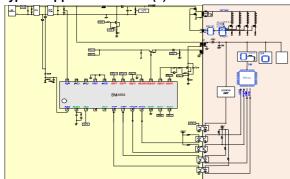

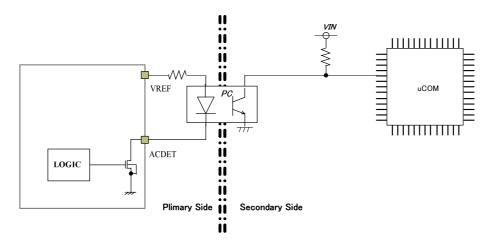

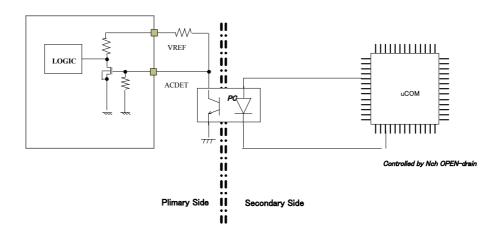

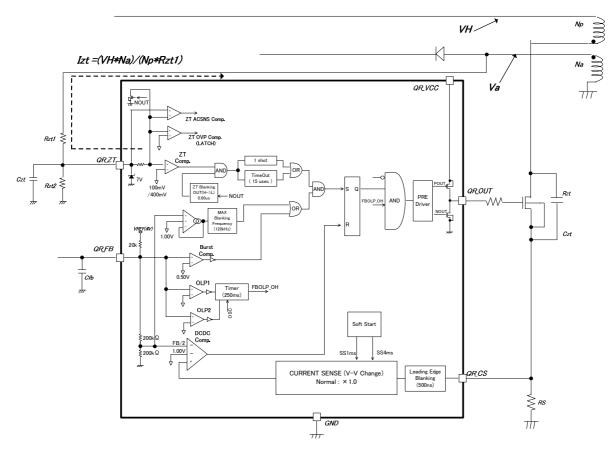

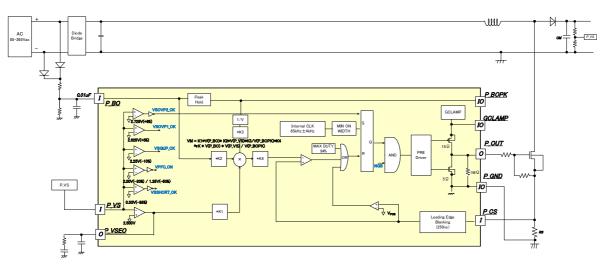

#### •Typical Application Circuit(s)

Figure 1. Application circuit

## OProduct structure : Silicon monolithic integrated circuit OThis product is not designed for protection against radioactive rays

# TSZ02201-0F2F0A200140-1-2 25.MAR.2013 Rev.001

#### Features

- Quasi-resonant circuit + PFC circuit

- Built-in HV Starter circuit

- Low consumption current (typ.10uA) when starter circuit is OFF.

heet

- Quasi resonant circuit Max operating frequency(120kHz) Frequency reduction function Over-current limiting variable function Pulse-by-pulse over-current protection circuit Built-in Soft start Voltage protection function (brown out) during low input ZT pin Over Voltage Protection Output overload protection (auto recovery /latch switching enabled) 250nsec Leading-Edge Blanking

- Power Factor Correction circuit Peak current control (65kHz) Frequency hopping function Per-cycle over current protection circuit Maximum power revision the multiplier with a revision circuit when the AC voltage falls the load change measure circuit

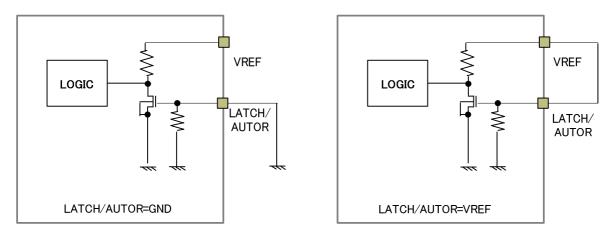

- Selectable protection method by LATCH/AUTOR terminal. LATCH/AUTOR=H : Latch

- LATCH/AUTOR=L : Auto recovery

- External stop function (COMP pin)

- AC input voltage stop detected function (ACDET)

- Built-in PFC stop terminal (PFCON/OFF)

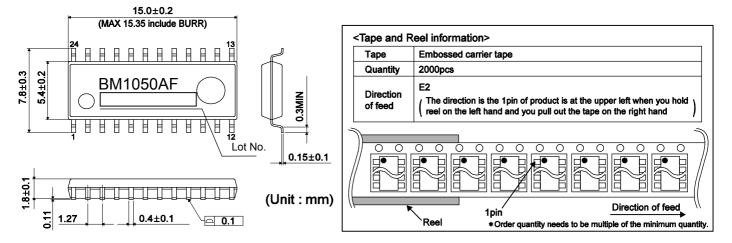

#### Package(s)

SOP24 15.0mm × 5.40mm × 1.80mm pitch1.27mm (Typ.) (Typ.) (TYP.) (TYP.)

## Applications

TV, AC adapters, printers, LED lighting

## ●Absolute Maximum Ratings (Ta = 25°C)

| Parameter                    | Symbol            | Rating        | Unit | Conditions                                                                                                    |

|------------------------------|-------------------|---------------|------|---------------------------------------------------------------------------------------------------------------|

| Maximum applied voltage 1    | Vmax1             | 650           | V    | VH_IN                                                                                                         |

| Maximum applied voltage 2    | Vmax2             | 30            | V    | VCC, QR_SEL                                                                                                   |

| Maximum applied voltage 3    | Vmax3             | 5.5           | V    | P_BO, P_VSEO, P_VS, P_BOPK<br>P_CS,PFCON/OFF,COMP,<br>ACDET, ACTIMER,QR_CS, QR_ZT,<br>QR_FB,LATCH/AUTOR, VREF |

| Maximum applied voltage 4    | Vmax4             | 15            | V    | GCLAMP, P_OUT, QR_OUT                                                                                         |

| output peak current 1        | I <sub>он</sub>   | -0.5          | Α    | QR_OUT, P_OUT                                                                                                 |

| output peak current 2        | I <sub>OL</sub>   | 1.0           | Α    | QR_OUT, P_OUT                                                                                                 |

| QR_ZT pin current 1          | I <sub>SZT1</sub> | -2.0          | mA   |                                                                                                               |

| QR_ZT pin current 2          | I <sub>SZT2</sub> | 3.0           | mA   |                                                                                                               |

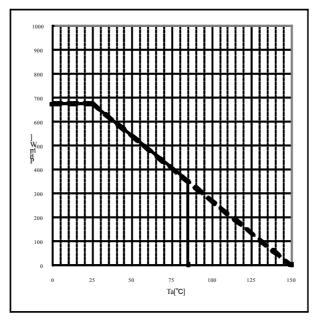

| Allowable dissipation        | Pd                | 687.6 (Note1) | mW   |                                                                                                               |

| Operating temperature range  | Topr              | -40 ~ +85     | °C   |                                                                                                               |

| Maximum junction temperature | Tjmax             | 150           | °C   |                                                                                                               |

| Storage temperature range    | Tstr              | -55 ~ +150    | °C   |                                                                                                               |

(Note1) When mounted (on 70 mm × 70 mm, 1.6 mm thick, glass epoxy on single-layer substrate). Reduce to 5.5 mW/°C when Ta =  $25^{\circ}$ C or above.

#### • Operating Conditions (Ta = $25^{\circ}$ C)

| Parameter                    | Symbol | Rating   | Unit | Conditions |

|------------------------------|--------|----------|------|------------|

| Power supply voltage range 1 | VCC    | 8.5~24.0 | V    | VCC        |

| Power supply voltage range 2 | VH_IN  | 80~600   | V    | VH_IN      |

| Power supply voltage range 3 | P_BO   | 0.0~1.8  | V    | P_BO       |

## • Electrical Characteristics (Unless otherwise noted, Ta=25, VH\_IN=320Vdc, VCC=12V)

| Parameter                                                      | Symbol                               | S                | pecifications    | ;                | ,<br>Unit | Conditions                                                                           |

|----------------------------------------------------------------|--------------------------------------|------------------|------------------|------------------|-----------|--------------------------------------------------------------------------------------|

|                                                                | Symbol                               | Minimum          | Standard         | Maximum          | Offic     | Conditions                                                                           |

| [Circuit current]                                              |                                      |                  |                  |                  |           |                                                                                      |

| Circuit current (ON) 1                                         | I <sub>on1</sub>                     | 0.700            | 1.200            | 1.700            | mA        | VCC=12.0V<br>(QR=ON, PFC=OFF)<br>QR_FB=1.0V<br>(during pulse operation)              |

| Circuit current (ON) 2                                         | I <sub>ON2</sub>                     | 0.700            | 1.000            | 1.300            | mA        | VCC=12.0V<br>(QR =ON, PFC=OFF)<br>QR_FB=VREF<br>(during pulse operation<br>when OFF) |

| Circuit current (ON) 3                                         | I <sub>ons</sub>                     | 0.800            | 1.800            | 2.800            | mA        | VCC=12.0V<br>(QR =ON, PFC=ON)<br>QR_FB=1.0V<br>(during pulse operation)              |

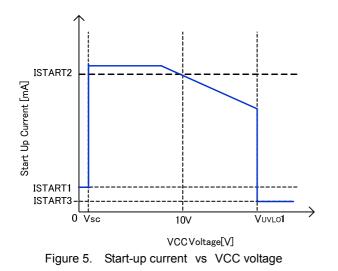

| [Start circuit Block]                                          | -                                    |                  |                  |                  |           |                                                                                      |

| Start current 1                                                | I <sub>START1</sub>                  | 0.100            | 0.500            | 1.000            | mA        | VCC= 0V                                                                              |

| Start current 2                                                | START2                               | 1.000            | 3.000            | 5.000            | mA        | VCC=10V                                                                              |

| OFF Current                                                    | I <sub>start3</sub>                  | -                | 10               | 16               | uA        | Input current from VH_IN<br>terminal after releasing<br>UVLO                         |

| VH voltage switched<br>start current                           | V <sub>sc</sub>                      | 0.400            | 0.800            | 1.400            | V         |                                                                                      |

| [VREF Block]                                                   |                                      |                  |                  |                  |           |                                                                                      |

| VREF output voltage                                            | $V_{\text{REF1}}$                    | 3.500            | 4.000            | 4.500            | V         |                                                                                      |

| VREF output capacitor                                          |                                      | 0.68             | 1.00             | 2.20             | uF        |                                                                                      |

| GCLAMP voltage 1                                               | GCL1                                 | 11.0             | 12.5             | 14.0             | V         | VCC=15V                                                                              |

| GCLAMP voltage 2                                               | GCL2                                 | 11.0             | 12.5             | 14.0             | V         | VCC=22V                                                                              |

| VREF UVLO 1                                                    | $V_{RUVLO1}$                         | 77.5<br>(3.100V) | 87.5<br>(3.500V) | 97.5<br>(3.900V) | %         | When VREF rise<br>The ratio of VREF pin<br>voltage.                                  |

| VREF UVLO 2                                                    | V <sub>RUVLO2</sub>                  | 52.5<br>(2.100V) | 62.5<br>(2.500V) | 72.5<br>(2.900V) | %         | When VREF drop<br>The ratio of VREF pin<br>voltage.                                  |

| VREF UVLO hysteresis                                           | $V_{RUVLO3}$                         | -                | 25<br>(1.000V)   | -                | %         | V <sub>RUVLO3</sub> = V <sub>RUVLO1</sub> - V <sub>RUVLO2</sub>                      |

| VCC UVLO voltage 1                                             | V <sub>UVL01</sub>                   | 12.50            | 13.50            | 14.50            | V         | VCC rise                                                                             |

| VCC UVLO voltage 2                                             | V <sub>UVLO2</sub>                   | 5.50             | 7.00             | 8.50             | V         | VCC drop                                                                             |

| VCC UVLO hysteresis                                            | V <sub>UVLO3</sub>                   | -                | 6.50             | -                | V         | V <sub>UVLO3</sub> = V <sub>UVLO1</sub> - V <sub>UVLO2</sub>                         |

| VCC OVP voltage 1                                              | V <sub>OVP1</sub>                    | 24.0             | 27.0             | 30.0             | V         | VCC rise                                                                             |

| VCC OVP voltage 2                                              | V <sub>OVP2</sub>                    | 20.0             | 23.0             | 26.0             | V         | VCC drop                                                                             |

| VCC OVP hysteresis<br>Brown out detection voltage 1            | V <sub>OVP3</sub>                    | - 0.350          | 4.0<br>0.400     | - 0.450          | V<br>V    | V <sub>OVP3</sub> = V <sub>OVP1</sub> - V <sub>OVP2</sub><br>P BO rise               |

| Brown out detection voltage 1<br>Brown out detection voltage 2 | V <sub>B01</sub><br>V <sub>B02</sub> | - 0.350          | 0.400            | - 0.450          | V         | P_BO fise<br>P BO drop                                                               |

| Brown out hysteresis                                           | V <sub>BO2</sub>                     | _                | 0.200            | -                | V         | $V_{B03} = V_{B01} - V_{B02}$                                                        |

| Brown out detection                                            |                                      |                  |                  |                  | v         | Times until ACDET logic                                                              |

| delay time 1                                                   | T <sub>BO1</sub>                     | 21.8             | 32.0             | 42.2             | ms        | change (ACTIMER=L)                                                                   |

| Brown out detection delay time 2                               | T <sub>BO2</sub>                     | 87.0             | 128.0            | 169.0            | ms        | Times until ACDET logic<br>change ( ACTIMER=H)                                       |

| Brown out detection delay time 3                               | T <sub>BO3</sub>                     | 170              | 250              | 330              | ms        | Times until PFC and QR stop                                                          |

## • Electrical Characteristics (Unless otherwise noted ,Ta=25,VH\_IN=320Vdc,VCC=12V)

| Parameter                                  | Symbol                          |         | Specifications          | ,       | Unit | Conditions |  |  |  |  |  |  |

|--------------------------------------------|---------------------------------|---------|-------------------------|---------|------|------------|--|--|--|--|--|--|

| Farameter                                  | Symbol                          | Minimum | Standard                | Maximum | Unit | Conditions |  |  |  |  |  |  |

| [ACDET pin characteristics]                |                                 |         |                         |         |      |            |  |  |  |  |  |  |

| ACDET pin ON resister                      | RACDET                          | 50      | 100                     | 200     | Ω    |            |  |  |  |  |  |  |

| [ACTIMER pin characteristics]              | ]                               |         |                         |         |      |            |  |  |  |  |  |  |

| ACTIMER pin input L level                  |                                 | -       | -                       | 0.3     | V    |            |  |  |  |  |  |  |

| ACTIMER pin input H level                  | VACTIMEH                        | 1.2     | -                       | -       | V    |            |  |  |  |  |  |  |

| ACTIMER pin                                | RACTIMEH                        | 165     | 330                     | 500     | kΩ   |            |  |  |  |  |  |  |

| pull-down resistor                         |                                 | 105     | 330                     | 500     | K77  |            |  |  |  |  |  |  |

| -                                          | [PFCON/OFF pin characteristics] |         |                         |         |      |            |  |  |  |  |  |  |

| PFCON/OFF pin input L level                | V <sub>PON/OFFL</sub>           | -       | -                       | 0.3     | V    | PFC = ON   |  |  |  |  |  |  |

| PFCON/OFF pin input H level                | $V_{\text{PON/OFFH}}$           | 1.2     | -                       | -       | V    | PFC = OFF  |  |  |  |  |  |  |

| PFCON/OFF pin                              | R <sub>PON/OFFH</sub>           | 50      | 100                     | 150     | kΩ   |            |  |  |  |  |  |  |

| pull-down resistor                         |                                 |         |                         |         |      |            |  |  |  |  |  |  |

| PFCON/OFF pin timer time                   | T <sub>PFCON/OFF</sub>          | 0.50    | 1.50                    | 3.00    | ms   |            |  |  |  |  |  |  |

| [LATCH/AUTOR pin characteri                | stics                           |         | 1                       |         |      |            |  |  |  |  |  |  |

| LATCH/AUTOR pin                            |                                 | -       | -                       | 0.3     | V    |            |  |  |  |  |  |  |

| input L level                              | • MODEL                         |         |                         | 0.0     | •    |            |  |  |  |  |  |  |

| LATCH/AUTOR pin                            | $V_{MODEH}$                     | 1.2     | -                       | -       | V    |            |  |  |  |  |  |  |

| input H level                              |                                 |         |                         |         |      |            |  |  |  |  |  |  |

| LATCH/AUTOR pin<br>pull-down resistor      | RMODEH                          | 50      | 100                     | 150     | kΩ   |            |  |  |  |  |  |  |

|                                            |                                 |         |                         |         |      |            |  |  |  |  |  |  |

| [COMP pin characteristics]                 |                                 |         |                         |         |      |            |  |  |  |  |  |  |

| COMP pin detection voltage                 | V <sub>COMP</sub>               | 0.370   | 0.500                   | 0.630   | V    |            |  |  |  |  |  |  |

| COMP pin pull-up resistor                  | R <sub>COMP</sub>               | 19.4    | 25.9                    | 32.3    | kΩ   |            |  |  |  |  |  |  |

| External Thermistor resistor               | R⊤                              | 3.32    | 3.70                    | 4.08    | kΩ   |            |  |  |  |  |  |  |

| Latch release voltage<br>(VCC pin voltage) | VLATCHOFF                       | -       | V <sub>UVL02</sub> -0.5 | -       | V    |            |  |  |  |  |  |  |

| Latch mask time                            | T <sub>COMP</sub>               | 70      | 150                     | 240     | us   |            |  |  |  |  |  |  |

#### ●Electrical Characteristics (Unless otherwise noted Ta=25, VH IN=320Vdc, VCC=12V)

| Parameter                                        | Symbol              |             | Specifications |         | Unit    | Conditions                                                   |

|--------------------------------------------------|---------------------|-------------|----------------|---------|---------|--------------------------------------------------------------|

|                                                  | 0,11201             | Minimum     | Standard       | Maximum | •       |                                                              |

| [Quasi-resonant Control Blo                      | ock]                |             |                |         |         |                                                              |

| [Quasi-resonant DC/DC con                        | verter Block        | (turn off)] |                |         |         |                                                              |

| QR_FB pin pull-up resistance                     | R <sub>FB</sub>     | 15          | 20             | 25      | kΩ      |                                                              |

| CS over-current<br>detect voltage 1A             | V <sub>lim1A</sub>  | 0.950       | 1.000          | 1.050   | V       | QR_FB=2.2V (AC=100V)                                         |

| CS over-current<br>detect voltage 1B             | $V_{lim1B}$         | 0.630       | 0.700          | 0.770   | V       | QR_FB=2.2V (AC=230V)                                         |

| CS over-current<br>detect voltage 1C             | $V_{lim1C}$         | -           | 0.250          | -       | V       | QR_FB=2.2V (AC=100V)<br>SoftStart1(~1ms)                     |

| CS over-current<br>detect voltage 1D             | V <sub>lim1D</sub>  | -           | 0.750          | -       | V       | QR_FB=2.2V (AC=100V)<br>Power limit1(1ms~PFC start)          |

| CS over-current<br>detect voltage 2A             | V <sub>lim2A</sub>  | -           | 0.250          | -       | V       | QR_FB=0.3V (AC=100V)                                         |

| CS switched ZT current                           | I <sub>ZT</sub>     | 0.800       | 1.000          | 1.200   | mA      |                                                              |

| CS Leading<br>Edge Blanking time                 | TLEB                | -           | 0.250          | -       | us      |                                                              |

| Turn off time                                    |                     | -           | 0.250          | -       | us      | *1                                                           |

| Minimum ON width                                 | $T_{min}$           | -           | 0.500          | -       | us      | T <sub>leb</sub> +T <sub>off</sub>                           |

| [Quasi-resonant DC/DC conv                       | /erter Block        | (turn on)]  |                |         |         |                                                              |

| Maximum operating<br>frequency 1                 | F <sub>sw1</sub>    | 106         | 120            | 134     | KHz     | QR_FB=2.00V                                                  |

| Maximum operating<br>frequency 2                 | $F_{SW2}$           | 24          | 30             | 36      | KHz     | QR_FB=0.50V                                                  |

| Frequency reduction<br>start FB voltage          | $V_{\text{FBSW1}}$  | 1.400       | 1.500          | 1.600   | V       |                                                              |

| Frequency reduction<br>end FB voltage            | $V_{\text{FBSW2}}$  | 0.45        | 0.65           | 0.85    | V       |                                                              |

| Voltage gain                                     | $AV_{cs}$           | 1.70        | 2.00           | 2.30    | V/V     | ⊿V (QR_FB)/⊿V<br>(QR_CS)                                     |

| ZT comparator voltage 1                          | V <sub>ZT1</sub>    | 60          | 100            | 140     | mV      | QR_ZT drop                                                   |

| ZT comparator voltage 2                          | V <sub>ZT2</sub>    | 300         | 400            | 500     | mV      | QR_ZT rise                                                   |

| ZT trigger timeout period                        | T <sub>ztout</sub>  | -           | 15             | -       | US      | Count from final ZT trigger                                  |

| [Quasi-resonant DC/DC con<br>Soft start time     | T <sub>ss</sub>     | 0.60        | nsj<br>1.00    | 1.40    | me      |                                                              |

| FB OLP Voltage 1a                                | V <sub>FOLP1A</sub> | 2.5         | 2.8            | 3.1     | ms<br>V | Operate QR FB rise                                           |

| FB OLP Voltage 1b                                | V <sub>FOLP1B</sub> | -           | 2.6            | -       | V       | Operate QR_FB drop                                           |

| FB OLP Voltage 2a                                | V <sub>FOLP2A</sub> | 3.3         | 3.6            | 3.9     | V       | Switched latch / Auto<br>recovery rise                       |

| FB OLP Voltage 2b                                | $V_{\text{FOLP2B}}$ | -           | 3.4            | -       | V       | Switched latch / Auto<br>recovery drop                       |

| FB OLP mode switched external connected resistor | $R_{FOLP2}$         | 90          | 100            | 110     | kΩ      | QR_FB pin externa<br>resistance value (during<br>latch mode) |

| FB OLP timer                                     | T <sub>FOLP</sub>   | 44          | 64             | 84      | ms      |                                                              |

| ZT OVP Voltage                                   | V <sub>ZTL</sub>    | 3.2         | 3.5            | 3.8     | V       |                                                              |

| [QR_OUT pin]                                     |                     |             |                |         |         |                                                              |

| QR_OUT pin<br>PMOS ON resistor                   | R <sub>POUT</sub>   | 5           | 15             | 30      | Ω       |                                                              |

| QR_OUT pin<br>NMOS ON resistor                   | R <sub>NOUT</sub>   | 2           | 5              | 10      | Ω       |                                                              |

| [QR_SEL pin]                                     |                     |             |                |         |         |                                                              |

| QR SEL pin Ron                                   | RMASK               | -           | 150            | _       | Ω       |                                                              |

\*1 Pulse is applied to QR\_CS pin\*2 Pulse is applied to QR\_ZT pin

| Parameter                              | Symbol                |                | Specifications |         | Unit     | Conditions |

|----------------------------------------|-----------------------|----------------|----------------|---------|----------|------------|

| i didineter                            | Cymbol                | Minimum        | Standard       | Maximum | Onit     | Conditions |

| [Power Factor Correction (PFC          | controlle)            | r block]       |                |         |          |            |

| [Power Factor Correction (Pl           | <sup>=</sup> C) Gm am | plifier block] |                |         |          |            |

| P_VS pin pull-up current               | I <sub>P_VS</sub>     | -              | 0.50           | -       | uA       |            |

| Gm amplifier normal voltage            | VVSAMP                | 2.460          | 2.500          | 2.540   | V        |            |

| Gm amplifier<br>trans-conductance      | $V_{\text{VSGM}}$     | 30.8           | 44.0           | 57.2    | uS       |            |

| Maximum Gm amplifier<br>source current | I <sub>VSAMP1</sub>   | 15             | 25             | 35      | uA       | P_VS=1.0V  |

| Maximum Gm amplifier<br>sink current   | I <sub>VSAMP2</sub>   | 24             | 40             | 56      | uA       | P_VS=3.5V  |

| [Power Factor Correction (PI           | FC) input v           | oltage monit   | or block]      |         |          |            |

| P BO input voltage range               | $V_{P_{BOIN}}$        | 0.000          | -              | 1.800   | V        |            |

| P BO pin leak current                  |                       | -1.00          | 0.00           | 1.00    | uA       |            |

| P_BOPK max charge current              | BOPKCHG               | 36             | 72             | 144     | uA       |            |

| P_BOPK max                             |                       | 0.1            | 0.2            | 0.4     | uA<br>uA |            |

| discharge current                      |                       |                |                |         |          |            |

| [Power Factor Correction (PI           | C) multipl            | ier block]     |                |         |          |            |

| Multiplier constant                    | K <sub>MULTI</sub>    | 0.37           | 0.54           | 0.71    |          |            |

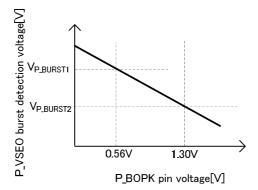

| P_VSEO stop voltage 1                  | V <sub>VSE01</sub>    | 181            | 226            | 271     | mV       | BOPK=0.56V |

| P_VSEO stop voltage 2                  | $V_{VSEO2}$           | 88             | 128            | 168     | mV       | BOPK=1.30V |

| [Power Factor Correction (Pl           |                       | tion frequen   | cy block]      |         |          |            |

| PFC Oscillation frequency              | F <sub>PSW1</sub>     | 60             | 65             | 70      | KHz      |            |

| PFC Frequency hopping width            | F <sub>PSWEL</sub>    | -              | 4.0            | -       | KHz      |            |

| PFC hopping frequency                  | F <sub>PCH</sub>      | 75             | 125            | 175     | Hz       |            |

| Minimum Pulse width                    | T <sub>min</sub>      | -              | 500            | -       | ns       |            |

| Maximum DUTY                           | D <sub>max</sub>      | 90.0           | 94.0           | 98.0    | %        |            |

| [Power Factor Correction (PF           |                       | lock]          |                | •       |          |            |

| P OUT pin PMOS ON resistor             | RPPOUT                | 5              | 15             | 30      | Ω        |            |

| P OUT pin NMOS ON resistor             | RP <sub>NOUT</sub>    | 2              | 5              | 10      | Ω        |            |

| P_OUT pin NMOS ON resistor             | <b>KP</b> NOUT        | 2              | 5              | 10      | Ω        |            |

## ● Electrical Characteristics (Unless otherwise noted Ta=25, VH\_IN=320Vdc, VCC=12V)

| Deremeter                               | Symbol                  | S               | Specifications   | 3               | ,<br>Linit | Conditions                                                       |

|-----------------------------------------|-------------------------|-----------------|------------------|-----------------|------------|------------------------------------------------------------------|

| Parameter                               | Symbol                  | Minimum         | Standard         | Maximum         | Unit       | Conditions                                                       |

| [Power Factor Correction (Pl            | <sup>=</sup> C) control | ler block ]     |                  |                 |            |                                                                  |

| [Power Factor Correction (PI            | C) protect              | ion function    | block ]          |                 |            |                                                                  |

| Leading Edge Blanking time              | T <sub>PLEB</sub>       | -               | 250              | -               | ns         |                                                                  |

| P_CS over current limit<br>voltage 1    | $V_{\text{PCS1}}$       | 0.93            | 1.16             | 1.40            | V          | P_BOPK=0.56V                                                     |

| P_CS over current limit<br>voltage 2    | $V_{\text{PCS2}}$       | 0.48            | 0.60             | 0.72            | V          | P_BOPK=1.30V                                                     |

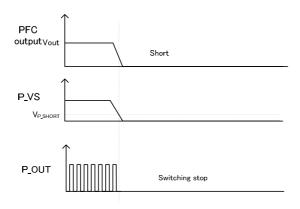

| P_VS short protection voltage           | $V_{P\_SHORT}$          | 0.200<br>(-92%) | 0.300<br>(-88%)  | 0.400<br>(-84%) | V          | Figure of () is comparison<br>with P_VS standard voltage<br>2.5V |

| QR power-limit P_VS voltage1            | $V_{\text{PFCON}}$      | 1.800<br>(-28%) | 2.000<br>(-20%)  | 2.200<br>(-12%) | V          | Figure of () is the ratio of<br>P_VS standard voltage 2.5V       |

| QR power limit P_VS voltage2            | $V_{\text{PFCOFF}}$     | 1.100<br>(-56%) | 1.250<br>(-50%)  | 1.400<br>(-44%) | V          | Figure of () is the ratio of<br>P_VS standard voltage 2.5V       |

| P_VS QR power<br>limit hysteresis       | $V_{\text{PFCHYS}}$     | -               | 0.750<br>(30%)   | -               | V          | Figure of () is the ratio of P_VS standard voltage 2.5V          |

| P_VS gain rise voltage                  | $V_{\text{PGUP}}$       | 2.050<br>(-18%) | 2. 250<br>(-10%) | 2.450<br>(-2%)  | V          | Figure of () is the ratio of P_VS standard voltage 2.5V          |

| P_VS gain fall voltage                  | $V_{\text{POVP1}}$      | -               | 2.625<br>(+5%)   | -               | V          | Figure of () is the ratio of<br>P_VS standard voltage 2.5V       |

| P_VS over voltage<br>protection voltage | $V_{POVP2}$             | -               | 2.725<br>(+9%)   | -               | V          | Figure of () is the ratio of P_VS standard voltage 2.5V          |

| P_VS over voltage<br>protection timer   | $T_{POVP2}$             | 16              | 32               | 48              | ms         | The time to detect P_VS over voltage protection                  |

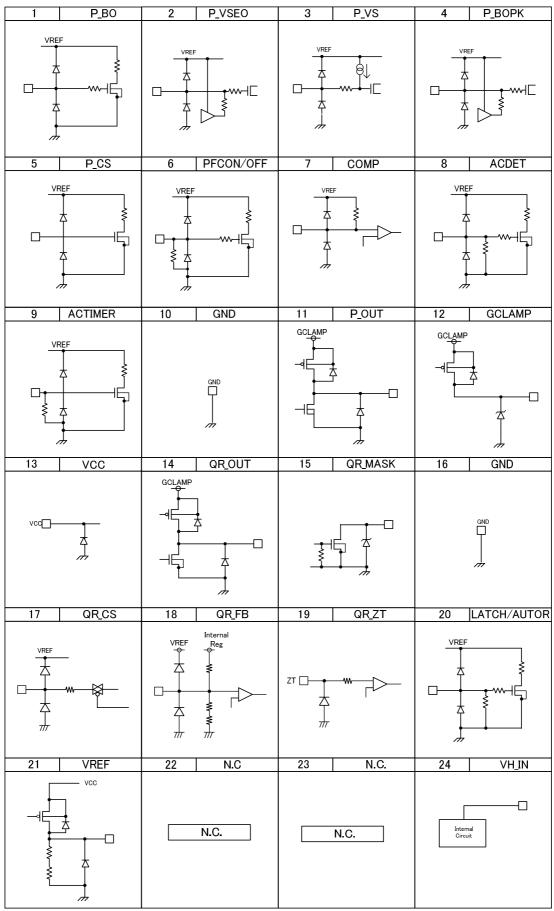

## PIN Configure

|    |             |     | Table 1. I/O Pin Functions                 |             |             |

|----|-------------|-----|--------------------------------------------|-------------|-------------|

| NO | PIN         | I/O | Function                                   | ESD protect | tion system |

| NO | PIN         | 1/0 | Function                                   | VCC         | GND         |

| 1  | P_BO        | I   | Input AC Voltage monitor pin               | 0           | 0           |

| 2  | P_VSEO      | I/O | PFC gm amplifier output pin                | 0           | 0           |

| 3  | P_VS        | I   | PFC Output voltage monitor pin             | 0           | 0           |

| 4  | P_BOPK      | 0   | Connected capacitor to the pin             | -           | -           |

| 5  | P_CS        | I   | PFC Coil current monitor pin               | 0           | 0           |

| 6  | PFCON/OFF   | I   | PFC ON/OFF control input pin               | 0           | 0           |

| 7  | COMP        | ļ   | External latch stop pin                    | 0           | 0           |

| 8  | ACDET       | 0   | Input AC voltage state communication pin   | 0           | 0           |

| 9  | ACTIMER     | ļ   | Brown out detection time setting input pin | 0           | 0           |

| 10 | GND         | I/O | GND                                        | 0           | -           |

| 11 | P_OUT       | 0   | PFC Output drive pin                       | 0           | 0           |

| 12 | GCLAMP      | I/O | Gate H level clamp pin                     | 0           | 0           |

| 13 | VCC         | I/O | Power supply pin                           | -           | 0           |

| 14 | QR_OUT      | 0   | Quasi-resonant Output drive pin            | 0           | 0           |

| 15 | QR_SEL      | 0   | Quasi-resonant Mask pin                    | -           | 0           |

| 16 | GND         | I/O | GND                                        | 0           | -           |

| 17 | QR_CS       | l   | Quasi-resonant Over current detected pin   | 0           | -           |

| 18 | QR_FB       | -   | Quasi-resonant Feedback detected pin       | 0           | 0           |

| 19 | QR_ZT       |     | Quasi-resonant Zero cross detected pin     | -           | 0           |

| 20 | LATCH/AUTOR | I   | Protection mode switched input pin         | 0           | 0           |

| 21 | VREF        | 0   | Internal power supply pin                  | 0           | 0           |

| 22 | -           | -   | -                                          | -           | -           |

| 23 | -           | -   | -                                          | -           | -           |

| 24 | VH_IN       | I   | AC Input voltage applied pin               | -           | -           |

## ●I/O Equivalent Circuit Diagram

Figure 2. I/O Equivalent Circuit Diagram

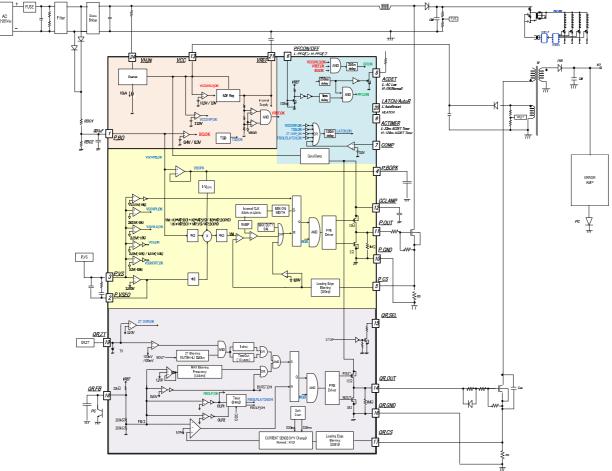

# Block Diagram

Figure 3. Block Diagram

## •Explanation of each block

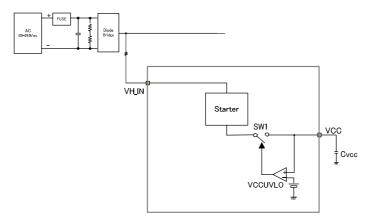

#### (1) Starter block (24pin)

BM1050AF built in the starter circuit that withstands 650V. For that, application used the IC is enabled faster start time and low standby power. After start-up, consumption power is idling current I<sub>START3</sub>(typ=10uA)only.

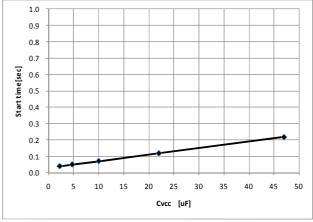

Reference of start-up time is shown in Figure 6.

It can start-up less than 0.1sec when  $C_{VCC}$ =10uF.

Figure 4. Start Circuit Block Diagram

Figure 6. Start time vs Cvcc (Reference values)

\*Start current flows from VH\_IN pin to VCC pin.

ex) When Vac=100V; consumption power of start-up circuit only. PVH=100V\* $\sqrt{2}$ \*10uA=1.41mW

ex) When Vac=240V; consumption power of start-up circuit only. PVH=240V\* $\sqrt{2}$ \*10uA=3.38mW

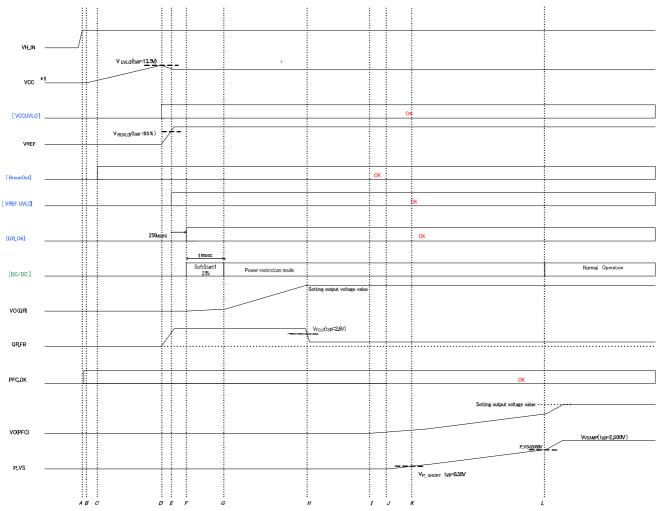

## (2) Start sequence

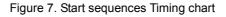

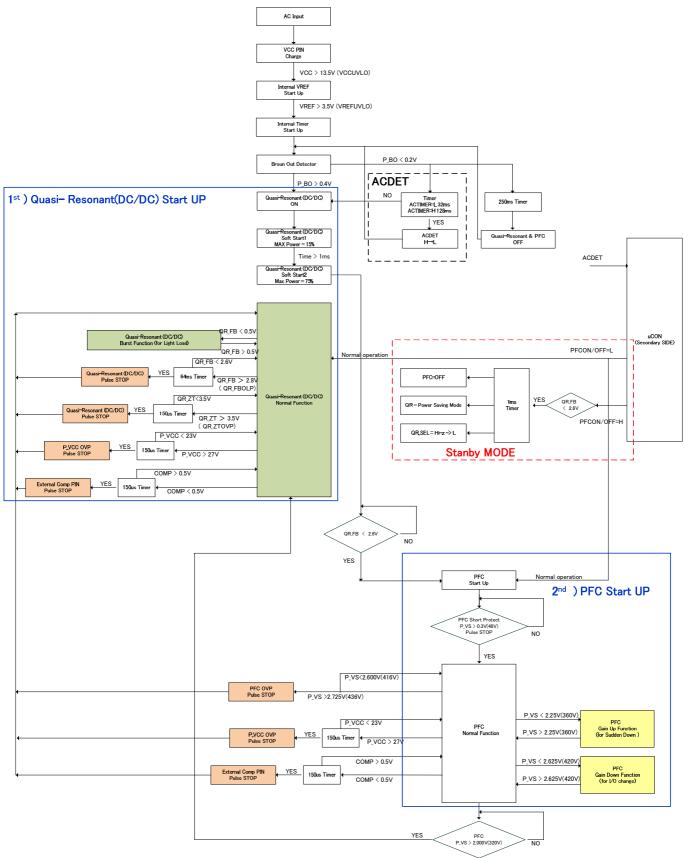

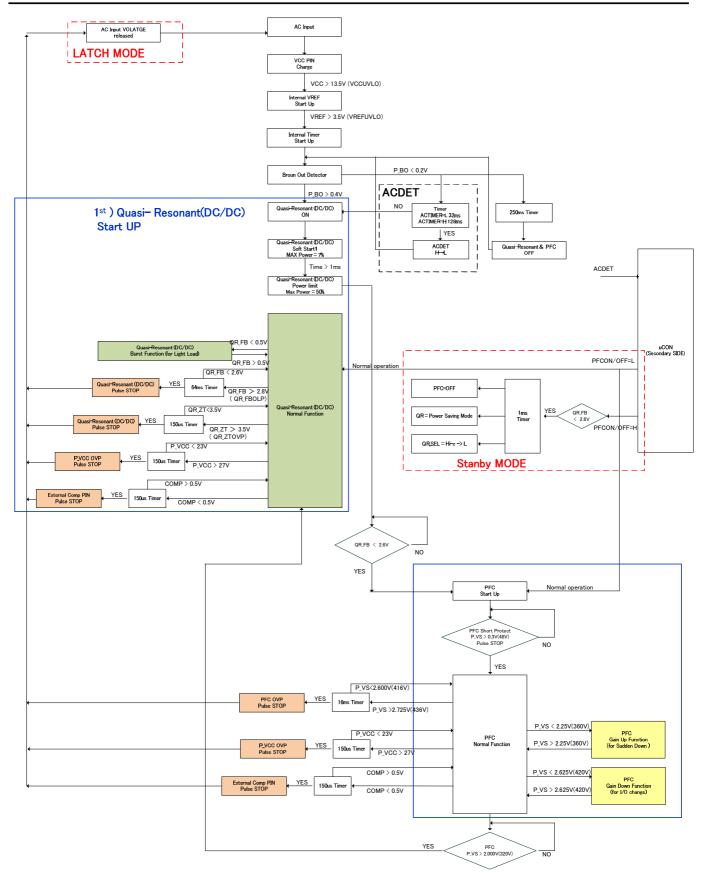

The start sequence of IC operates DC/DC part, next PFC part (See the figure 7).

- A : Input voltage VH is applied.

- B : Charge current flows from VH\_IN pin to the VCC pin capacitor. Then VCC pin voltage rises.

- C : Monitor the AC voltage by P\_BO pin. And confirm normal state by releasing brown out.

- D :When  $V_{UVLO1}$  (typ=13.5V) < VCC pin, release the inside UVLO and ON the inside regulator VREF.

- E : When  $V_{RUVLO1}$  (typ=87.5%) < VREF pin, release the inside VREFUVLO.

- F : If the 'E' state continues constant period, DC/DC part starts because it recognizes normal state. When the switching starts, VOUT voltage rises.

When the DC/DC start-up, please set external parts to be regulated output voltage within the  $T_{FOLP}$  period (64ms .typ ). [QR start-up operation]

- G: This IC adjusts over current limiter of DC/DC by operation of soft start 1 against over voltage and current rising. That term continues T<sub>ss1</sub> (typ=1ms).

- H: This IC adjusts over current limiter of DC/DC by operation of soft start 2 against over voltage and current rising. Soft start operation continues power limiter operation until P\_VS pin voltage > V<sub>PFCON</sub> (2.00V typ). This IC operates the state that maximum power of QR is 50% at this state.

- I: If secondary voltage is setting value, QR\_FB pin voltage is constant value corresponded load by current from photo coupler. At normal state, QR\_FB voltage is QR\_FB<V<sub>FBOLP1B</sub> (2.60V typ).

- [PFC start up operation]

- J: At the point in I time, This IC recognizes that the part of DC/DC operation is normal, Part of PFC starts operation.

- K: If P\_VS pin voltage is upper V<sub>P\_SHORT</sub> (typ = 0.3V), this IC judges short detection normal.

- L: P\_VSEO voltage rises from 0V to prevent from over rising voltage and current at PFC part.

- At this time P\_OUT pin DUTY increase from 0% with P\_VSEO voltage increasing.

About figure7, condition is PFCON/OFF=L.

Start up operation is shown at figure8, 9 by the state shift figure.

Figure 8 is LATCH/AUTOR=L (auto return operation), and figure 9 is LATCH/AUTOR=H (LATCH operation)

Figure8. Diagram of state machine (LATCH/AUTOR=L)

Figure 9. Diagram of state machine (LATCH/AUTOR=H)

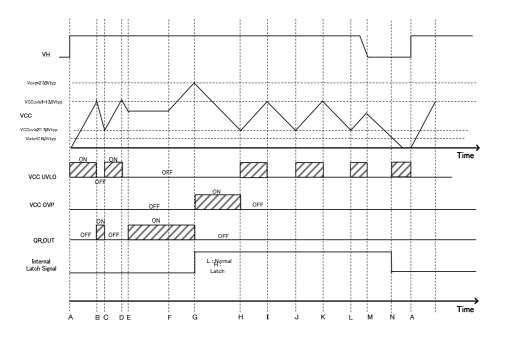

## (3) VCC protection function and VREF pin function

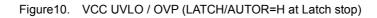

### (3-1) VCC pin protection function(13pin)

BM1050AF built in VCC low voltage protection function of VCCUVLO (Under Voltage Lock Out) and over voltage protection function of VCC OVP (Over Voltage Protection).

This function monitors VCC pin and prevent VCC pin from destroying switching MOSFET at abnormal voltage.

VCCUVLO is auto recovery comparator that has voltage hysteresis. VCCOVP operates as latch mode comparator in the LATCH/AUTOR=H and as auto return comparator in the LATCH/AUTOR=L.

VCC<V<sub>LATCHOFF</sub> (typ =  $V_{uvlo1} - 0.5$ ) is condition of latch release (reset) after detection of latch operation by VCCOVP. Refer to the operation figure 10.

VCCOVP built in mask time  $T_{COMP}$  (typ=150us), in case of continuing VCCOVP 150us, operates over voltage detection. By this function, this IC masks pin generated surge etc.

A:VH input, VCC voltage rise

B:VCC>Vuvlo1,DC/DC operation start

C:VCC<Vuvlo2,DC/DC operation stop

D:VCC>Vuvlo1,DC/DC operation start

E:VCC voltage decreases until starting DC/DC switching

#### F:VCC rise

F:When VCC>Vovp1,DC/DC operation is stopped. Switching is stopped by internal latch signal.

G:Then DC/DC operation is stopped, power supply is lost from auxiliary, VCC voltage downs.

H:VCC<Vuvlo2, P\_VCC voltage rises for dropping IC's consumption current.

I:VCC>Vuvlo1, this IC dose not operate DC/DC for latch operation. VCC voltage drops because of dropping of IC's consumption current.

J:same of H

K:same of I

L:same of J

M:VH is open(the state is outlet out).VCC drops.

N:VCC  $< V_{COMP}$ , latch releases.

## (3-2) VREF pin function(21pin)

VREF pin is internal regulator output pin.

The use of VREF pin is IC's internal supply and connection of LATCH/AUTOR pin changing. This pin needs an external capacitance, please use the capacitance following table.

| Table 2 | VRFF | nin out | put ca | nacitor | capacitance |

|---------|------|---------|--------|---------|-------------|

|         |      | pintout | pulou  | paonor  | capacitance |

| Deremeter             | Queshal   | 0,      | Specification |         | Linit | Canditiana |

|-----------------------|-----------|---------|---------------|---------|-------|------------|

| Parameter             | Symbol    | Minimum | Standard      | Maximum | Unit  | Conditions |

| VREF Output Capacitor | $C_{REF}$ | 0.68    | 1.00          | 2.20    | uF    |            |

## (3-3) VREF pin protection function(21pin)

VREF pin built in low voltage protection function VREF UVLO (Under Voltage Protection). This IC prevents from error operating at the time, VREF starts up and VREF is low, by this function.

Figure 11. VREF UVLO Function

# BM1050AF-G

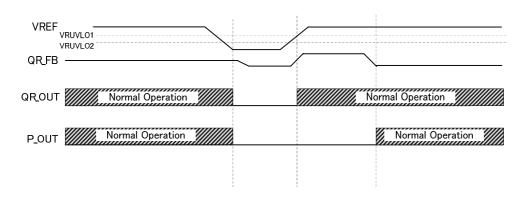

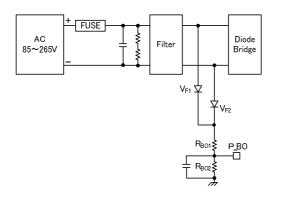

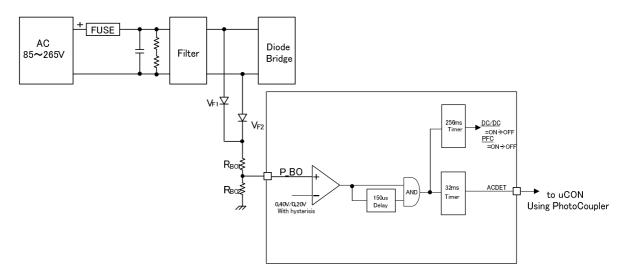

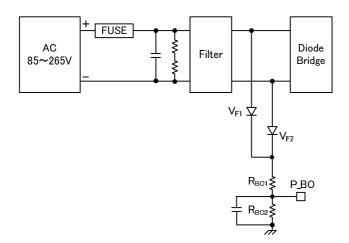

#### (3-4) Blown out function(1 pin)

BM1050AF built in blown out function. This function is that this IC stops DCDC operating at the time when input AC voltage is low. Show the example figure12. This IC divides input voltage by the resistance, and input P\_BO pin.

This IC detects from circuit normal state, and starts DC/DC operation the time when P\_BO pin exceeds Vbo1(0.4V typ).

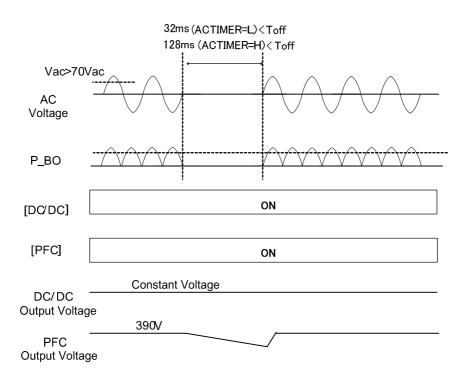

ACDET=L after TB01(typ.32ms) or Tb02(typ.128ms) from P\_BO pin drops from VB02(0.2V typ).

Moreover, if TB03 (typ.250ms) passes from P\_BO<VB02, DC/DC part and PFC part is stopped.

About every resistance of fugure12, because P\_BO pin is used PFC operation, please set  $R_{bo1}=4Mohm, R_{bo2}=16kohm$  for operating the range of P\_BO pin voltage 0~1.8V. In this case, by the following formula, P\_BO=0V~0.56V at the case AC100V, P\_BO=0V~1.237V at the case AC220V.

$$P\_BO = (\sqrt{2} \times V_{AC} \quad V_{F1}) \times \frac{R_{BO2}}{R_{BO1} + R_{BO2}}$$

Then

$$\sqrt{2} \times V_{AC} \gg V_{F1}$$

$$P_{BO} = \sqrt{2} \times V_{AC} \times \frac{R_{BO2}}{R_{BO1} + R_{BO2}}$$

Figure 12. Block Diagram of Blown out Function

Figure 13. Detection Way of Blown out Function

$$\begin{split} A: P\_BO > V_{BO1}(typ.0.4V) \ \ ACDET=L->H \\ B: After 150us from A DC/DC part starts up. \\ C:QR\_FB < V_{FCLP1B}(typ.2.6V). PFC part starts up. \\ D: If PFC output is larger than constant voltage, ACTIMER=L->H. \\ E: P\_BO < V_{BO2}(typ.0.2V) Timer start operation by detection blown out protection. \\ F:After T_{BO1}(typ.32ms) or T_{BO2}(typ.128ms) from E, ACDET=H->L. It is possible to set T_{BO1} and T_{BO2} at ACTIMER pin \\ \end{split}$$

G:After T<sub>B02</sub>(typ.250ms) from E, DC/DC part and PFC part are OFF

## (4)Controller part

#### (4-1)ACDET pin (8pin)

ACDET pin is NMOS open drain output. It monitors AC voltage, and is used for controlling secondary micon. Show the using example figure14, 15. Please set VIN is H voltage of micon.

- ACDET=L : Abnormal state (P\_BO < 0.2V)

- ACDET=H : Normal state

Figure14. Using Example of ACDET Pin

Figure15. Explanation of ACDET Pin

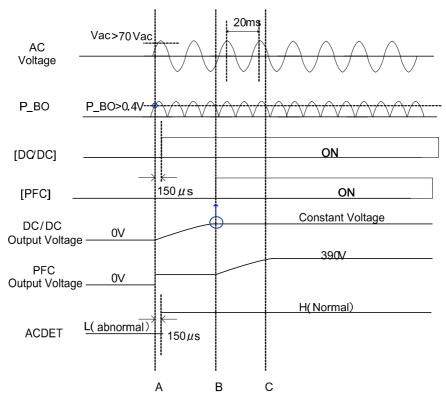

Next, show an easy sequence.

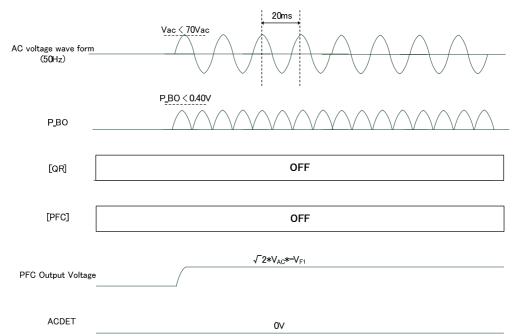

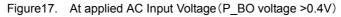

Figure16. At applied AC Input Voltage(P\_BO voltage<0.4V)

# Because P\_BO < 0.4V, DC/DC part is OFF.

VCC voltage>13.5V

A: Detect P\_BO>0.4V, Quasi resonance starts operation After 150µs

B:PFC start up

#### C: PFC output stabilized

\*About PFC operation, by the micon, is able to be controlled using PFCON/OFF pin.

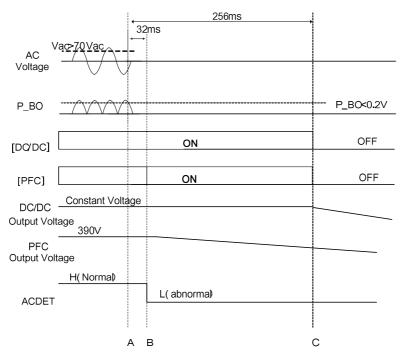

A:Detect P\_BO<0.2V, internal ACDET timer operates. At this time, output of PWC downs.

B:After 32ms (ACTIMER=L) from the point A, ACDET pin voltage is H->L, send to the  $\mu$ -controller abnormal signals. C:After 250ms from the point of A.PFC and Quasi Resonant are stopped

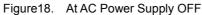

Figure 19. At AC Power Supply the case of operation moment stop

The case of AC voltage is OFF suddenly, constant area is masked.

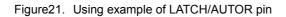

The time of constant area of masking is depends on ACTIMER pin.

The case of ACTIMER pin=L, Mask time=32ms, the case of ACTIMER pin=H, mask time=128ms.

The moment of AC voltage momentary power interruption, because PFC output voltage is down by corresponding to load, please watch out.

## (4-3) PFCON/OFF pin

PFCON/OFF pin is NMOS gate input pin. Refer to following the functions.

An internal timer is integrated for noise protection on PFCON/OFF pin.

After  $T_{PFCONOFF}$ (typ.1ms) from PFCON/OFF L $\rightarrow$ H, PFCON/OFF H operation starts. At PFCON/OFF H $\rightarrow$ L, internal timer is not integrated.

function1) PFC circuit operation is OFF control.

In order to reduce standby power, IC controls PFC part operation at PFCON/OFF pin.

function2)QR\_SEL pin is Hi-z $\rightarrow$ L

function3) DC/DC part is maximum power reducing mode.

Refer to example of using at figure 20.

PFCON/OFF=L : DC/DC part=ON、 PFC part=ON、 QR\_SEL=Hi-Z、 Maximum power reducing mode =Disable PFCON/OFF=H : DC/DC part=ON、 PFC part=OFF、 QR\_SEL=L、 Maximum power reducing mode =Enable

Figure 20. Using example of PFCON/OFF pin

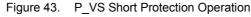

### (4-4) LATCH/AUTOR pin

LATCH/AUTOR pin is NMOS gate input pin. Refer to example of using at figure21. Operation setting of protection function is shown at table3.

LATCH/AUTOR=L : Auto recovery LATCH/AUTOR=H : Latch

|                          |                                                        |                                                              | LATCH/AU                                | JTOR=GND                      |                                         | LATCH/AUTOR                                                  |                                                  |                           |                                          |  |

|--------------------------|--------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------|-------------------------------|-----------------------------------------|--------------------------------------------------------------|--------------------------------------------------|---------------------------|------------------------------------------|--|

| ITEM                     | Contents                                               | detection<br>method                                          | operation<br>at detection               | release<br>mothod             | operaction<br>at detection              | detection<br>method                                          | operation<br>at detection                        | release<br>mothod         | operaction<br>at detection               |  |

| VREFUVLO                 | VREF PIN<br>Low voltage protection<br>function         | VREF<2.5V<br>(VREF falling)                                  | PFC part, DC/DC part operation stops    | VREF>3.5V<br>(VREFrising)     | PFC partDC/DC part<br>enable to operate | same as LATCH/AUTOR=GND                                      |                                                  |                           |                                          |  |

| VCCUVLO                  | VCC PIN<br>Low voltage protection<br>function          | VCC<7.0V<br>(VCC falling)                                    | PFC part, DC/DC<br>part operation stops | VCC>13.5V<br>(VCC rising)     | PFC partDC/DC part<br>enable to operate |                                                              | same as LATC                                     | H/AUTOR=GND               |                                          |  |

| VCCOVP                   | VCC PIN<br>Over voltage protection<br>function         | VCC>27V state<br>continues between<br>150us(VCC rising)      | PFC part, DC/DC<br>part operation stops | VCC<23.0V<br>(VCCfalling)     | PFC partDC/DC part<br>enable to operate | VCC>27V<br>(VCC rising)                                      | PFC part, DC/DC<br>part latch operation<br>stops | VCC<6.5V<br>(VCC falling) | PFC part, DC/DCpart<br>enable to operate |  |

| blown out                | Input AC voltage<br>Low voltage protection<br>function | P_BO<0.2V state<br>continues between<br>250ms(P_BOfalling)   | PFC part, DC/DC part operation stops    | P_BO>0.4V<br>(P_BOrising)     | PFC partDC/DC part<br>enable to operate |                                                              |                                                  |                           |                                          |  |

| QR_FB_OLP1               | QR_FB pin<br>Over current protection<br>function       | QR_FB>2.8V state<br>continues between<br>250ms(QR_FB         | DC/DC part<br>operation stops           | QR_FB<2.6V<br>(QR_FB falling) | normal operation                        | same as LATCH/AUTOR=GND                                      |                                                  |                           |                                          |  |

| QR_FB_OLP2               | QR_FB pin<br>Over current protection<br>function       | QR_FB>3.6V<br>(QR_FB rising)                                 | DC/DC part<br>operation stops           | QR_FB<3.4V<br>(QR_FB falling) | normal operation                        | same as LATCH/AUTOR-GND                                      |                                                  |                           |                                          |  |

| QR_ZT OVP                | QR_ZT pin<br>Over voltage protection<br>function       | QR_ZT>3.5V state<br>continues between<br>150us(QR_ZT rising) | DC/DC part<br>operation stops           | QR_ZT<3.5V<br>(QR_ZT falling) | normal operation                        | QR_ZT>3.5V state<br>continues between<br>150us(QR_ZT rising) | PFC part, DC/DC<br>part latch operation<br>stops | VCC<6.5V<br>(VCC falling) | normal operation                         |  |

| P_VS short<br>protection | P_VS pin<br>Short protection function                  | P_VS<0.30V<br>(P_VS falling)                                 | PFC part<br>operation stops             | P_VS>0.30V<br>(P_VS rising)   | normal operation                        | same as LATCH/AUTOR=GND                                      |                                                  |                           |                                          |  |

| P_VS GAIN<br>increasing  | P_VS pin<br>Low voltage gain<br>increasing function    | P_VS<2.25V<br>(P_VS falling)                                 | GM AMP GAIN<br>increasing               | P_VS>2.25V<br>(P_VS rising)   | normal operation                        | same as LATCH/AUTOR=GND                                      |                                                  |                           |                                          |  |

| P_VS OVP1                | P_VS pin<br>Over voltage protection<br>function1       | P_VS>2.625V<br>(P_VS rising)                                 | GM AMP GAIN<br>falling                  | P_VS<2.625V<br>(P_VS falling) | normal operation                        | same as LATCH/AUTOR=GND                                      |                                                  |                           |                                          |  |

| P_VS OVP2                | P_VS pin<br>Over voltage protection<br>function2       | P_VS>2.725V<br>(P_VS rising)                                 | PFC part、DC/DC<br>part operation stops  | P_VS<2.600V<br>(P_VS falling) | normal operation                        | P_VS>2.725V<br>(P_VS rising)                                 | PFC part, DC/DC<br>part latch operation<br>stops | VCC<6.5V<br>(VCC下降時)      | normal operation                         |  |

| COMP function            | COMP pin<br>Protection function                        | COMP<0.5V state<br>continues between<br>150us(COMP falling)  | PFC part, DC/DC<br>part operation stops | COMP>0.50V<br>(COMP rising)   | normal operation                        | COMP<0.5V state<br>continues between<br>150us(COMP falling)  | PFC part, DC/DC<br>part latch operation<br>stops | VCC<6.5V<br>(VCC falling) | normal operation                         |  |

#### Table 3. List of Protection Function Operation Setting by LATCH/AUTOR pin

\*Comparator level of protection function is shown by TYP value.

## (4-5) ACTIMER pin

ACTIMER pin is NMOS gate input pin. Show example of using figure 22, 23 Set the detect timer of AC voltage drop. (please refer to ACDET pin page)

Figure 22. Using example of ACTIMER pin

ACTIMER=GND : 32ms Timer ACTIMER=VREF :128ms Timer

Figure23. AC power at the case momentary power interruption OFF

## (4-6) COMP pin(external stop control function)

COMP pin is stop control pin. When COMP pin voltage drops from  $V_{\text{COMP}}$  (0.5V. typ), COMP pin stops PFC and DC/DC part operation.

This IC built in T<sub>COMP</sub> (150us .typ) until stopping switching, prevent from stopping by noise.

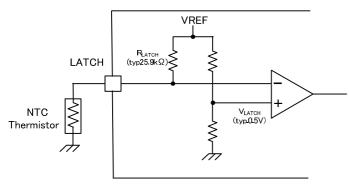

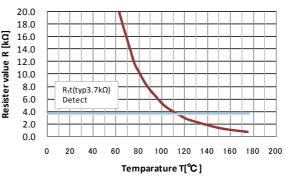

COMP pin is in pull-up resistor  $R_{COMP}$  (25.9k $\Omega$ . typ), When COMP pin is the state of pull-down with lower resistance than  $R_{\tau}(3.70k\Omega$ .typ), COMP pin detects abnormal. Show application examples at the figure24, 25, and 26.

#### Temperature protection by NTC thermister

By putting a thermister at the COMP pin, it is possible to stop latch on temperature rising. The case of this application, please design thermister resister is  $R_{\tau}(3.70k\Omega.typ)$  on temperature detection. (Figure24 and 25 is application circuit that latch on Ta=110°C)

Figure 24. Temperature Protection Application

Figure 25. Temperature–Thermistor Resistor characteristic

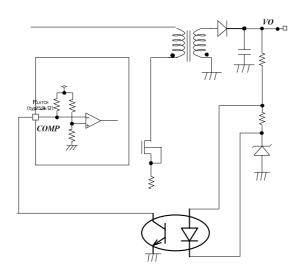

#### Secondary over- voltage protection

This IC can detect secondary over-voltage by putting photo coupler to COMP pin.

Figure 26. Output Over Voltage Protection Application

Table 4. Changes of COMP function Operation by LATCH/AUTOR pin

|               |          |                                                             | LATCH/AU                  | JTOR=GND                    |                            | LATCH/AUTOR=VREF    |                           |                               |                            |

|---------------|----------|-------------------------------------------------------------|---------------------------|-----------------------------|----------------------------|---------------------|---------------------------|-------------------------------|----------------------------|

| ITEM          | contents | detection<br>method                                         | operation<br>at detection | release<br>mothod           | operaetion<br>at detection | detection<br>method | operation<br>at detection | release<br>mothod             | operaction<br>at detection |

| COMP function | COMP pin | COMP<0.5V state<br>continues between<br>150us(COMP falling) |                           | COMP>0.50V<br>(COMP rising) | normal operation           |                     | part latch operation      | P_VCC<6.5V<br>(P_VCC falling) | normal operation           |

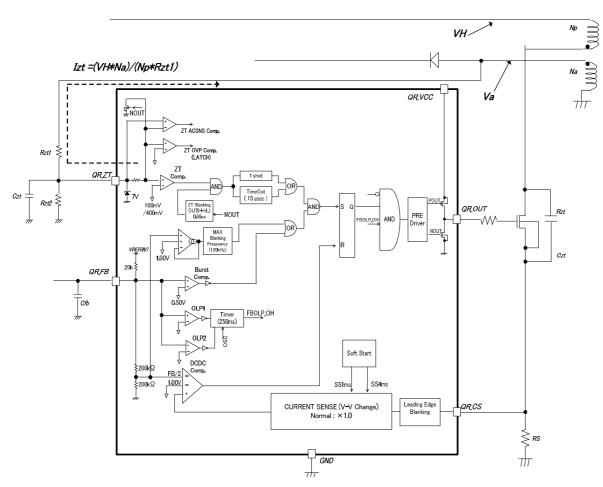

## (5)Quasi-Resonant DC/DC converter function

Part of quasi-resonant DC/DC uses PFM(Pulse Frequency Modulation)mode control.

The QR\_FB pin, QR\_ZT pin and QR\_CS pin are monitored to provide a system optimized for DC/DC."

The switching MOSFET ON width (turn OFF) is controlled via the QR\_FB pin and QR\_CS pin, and the OFF width(turn ON). Show following detail explanation. (refer to figure27).

Figure27. Diagram of Quasi-resonant DC/DC Operation

## (5-1) Determination of ON width (turn OFF)

ON width is controlled via the QR\_FB pin and QR\_CS pin.

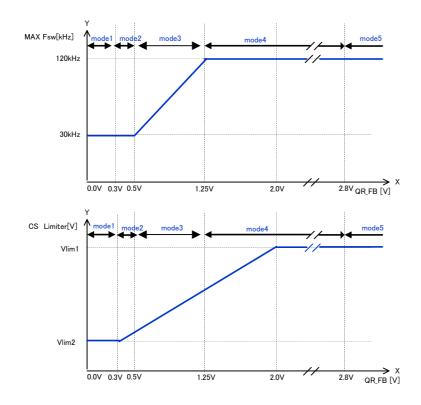

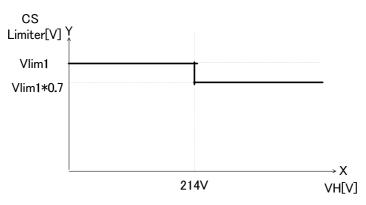

The QR\_FB pin voltage is compared with the IC internal voltage  $V_{lim1}$  (1.0V typ) and, as is shown in Figure 28. And the comparator level changes linearly.

The QR\_CS pin is also used for the pulse-by-pulse over current limiter circuit.

By changing voltage at the QR\_FB pin, DC/DC results in changes of the maximum blanking frequency and over-current limiter level.

mode1: Burst operation

·mode2: Frequency reduction operation(reduces maximum frequency)

mode3: Maximum frequency operation(operates at maximum frequency)

mode4: Overload operation(pulse operation is stopped when overload is detected)

Figure 28. Relation of QR\_FB pin, over current limiter and maximum frequency

The over current limiter level is adjusted, when the input voltage is changed, operate the soft start function. In this case, the Vlim1 and Vlim2 values are as listed below."

| Soft start    | AC=^            | 100V            | AC=230V         |                 |  |

|---------------|-----------------|-----------------|-----------------|-----------------|--|

|               | Vlim1           | Vlim2           | Vlim1           | Vlim2           |  |

| Start~1ms     | 0.250V ( 25.0%) | 0.039V ( 3.9%)  | 0.176V ( 17.6%) | 0.026V(2.6%)    |  |

| 1ms~PFC Start | 0.750V ( 75.0%) | 0.113V ( 11.3%) | 0.525V ( 52.5%) | 0.079V(7.9%)    |  |

| PFC Start~    | 1.000V (100.0%) | 0.150V ( 15.0%) | 0.700V ( 70.0%) | 0.105V ( 10.5%) |  |

| Table 5. er current protection voltage of Quasi-resonant DC/DC | С |

|----------------------------------------------------------------|---|

|----------------------------------------------------------------|---|

\*( ) is AC=100V, these show relative value of compare with  $V_{lim1}(1.0Vtyp)\,$  of normal operation.

This table is separated AC100V and AC230V for the function of QR\_CS current changing function that is shown (4-3).

## (5-2)LEB(Leading Edge Blanking)function

When the switching MOSFET is turned ON, surge current occurs at each capacitor charge /discharge or drive current.

For that, QR\_CS voltage rise temporarily, over current limiter may be detected errors.

To prevent detection errors blanking time is built in to mask  $T_{LEB}$  (typ=250ns).

This blanking function enables a reduction of CS pin filtering.

#### (5-3) CS over current protection function

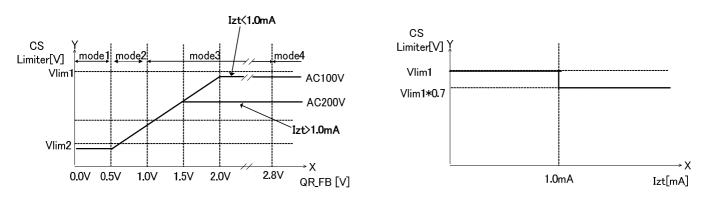

When the AC input voltage (VHIN) is high, the ON time is reduced and the operating frequency increases. As a result, the maximum rated power is increased for a constant over current limiter level. As a countermeasure, DC/DC is switched over current detected level.

AC input voltage detection method is that monitoring QR\_ZT current.

When MOSFET is turn ON, the auxiliary voltage (Va) is the minus voltage that depends on input voltage (VH).

QR\_ZT pin is clamped about 0V internal IC.

Following is the formula for that case.

Refer to the block figure29. See the graph figure30 and 31.

$Izt = (V_a - V_{zt})/R_{zt1} = VH * N_a/N_p / R_{zt1}$

#### Rzt1 = Va/Izt

For that, VH voltage is set by the resistance value of R<sub>zt1</sub>. Then, QR\_ZT bottom detection voltage is decided, Please set timing by C<sub>zt</sub>.

Figure 29. Diagram of CS switching current

Figure 30. QR\_CS Switching QR\_FB Voltage VS QR\_CS Voltage Figure 31. QR\_CS Switching Izt Current VS QR\_CS Voltage

ex) setting method (operate changing AC100V and AC220V) AC100V 141V $\pm$ 42V( $\pm$ 30% margin) AC220V 308V $\pm$ 62V( $\pm$ 20% margin) The case of above, Between 182V $\sim$ 246V, operates changing of CS current => Operate VH=214VH Np=100, Na=15

$$\label{eq:Va} \begin{split} &Va{=}Vin^*Na/Np = 214V^*15/100~^*({-}1) = {-}32.1V \\ &Rzc = Va/I_{z\tau} = {-}32.1V/{-}1mA = 32.1k\Omega \end{split}$$

By the above explanation, Rzt=32K $\Omega$

Figure 32. Example of Over current limiter of CS switching

## (5-4) Determination of OFF width(turn ON)

OFF width is controlled at the QR\_ZT pin.

When switching is OFF, the power stored in the coil is supplied to the secondary-side output capacitor.

When this power supply ends there is no more current flowing to secondary side, so the switching MOS drain pin voltage drops. Consequently, the voltage on the auxiliary coil side also drops.

A voltage that was resistance-divided from the QR\_ZT pin by Rzt1 and Rat2 is applied. When this voltage level drops to Vzt1(100mV typ) or below, switching is turned ON the QR\_ZT comparator. Since bottom status is detected at the QR\_ZT pin, time constants are generated using Czt, Rzt1, and Rzt2.

Additionally, a QR\_ZT trigger mask function (described in section 5-5) and a QR\_ZT time out function (described in section 5-6) are built in.

### (5-5)QR ZT trigger mask function

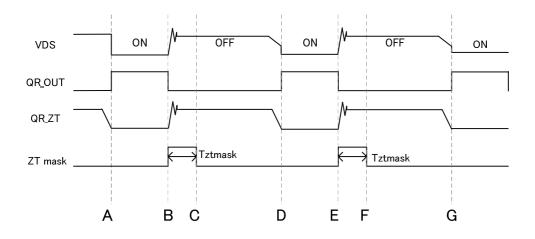

The QR\_ZT trigger mask function is shown below figure33.

When switching is set ON -> OFF, super position of noise may occur at the QR\_ZT pin.

At such times, the QR\_ZT comparator is masked for the  $T_{ztmask}$  time to prevent QR\_ZT comparator operation errors.

Figure 33. ZT trigger mask Function

- A: QR\_OUT OFF=>ON

- B: QR OUT ON=>OFF

- C: Because of generation of QR\_ZT pin noise, T<sub>ZTMASK</sub> doesn't operate the QR\_ZT comparator.

- D: Same as A

- E: Same as B

- F: Same as C

- G: Same as A

## (5-6)ZT time out function(Figeure34)

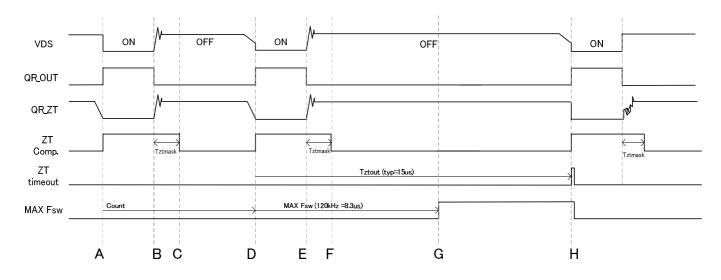

After the ZT comparator is detected, this function forcibly turns switching ON if the following is not detected, even when  $T_{ztout}$  (15us typ) has elapsed.

If, the secondary output voltage is low, the auxiliary coil voltage VA is reduced, and the QR\_ZT pin voltage drops below  $V_{zt1}$  (100mVtyp).

In such cases, this function turns switching ON forcibly.

As for  $T_{ztout}$ , since 15 us (typ) = 66.7kHz, when the maximum frequency is in frequency reduction mode, the QR\_ZT timeout time depends on the frequency reduction mode

Figure 34. ZT Time out Function

- A:  $QR_{ZT} < V_{ZT1}$ , DC/DC is ON. Count maximum frequency at this point.

- B: DC/DC ON=>OFF

- C: Because noise is generated at QR\_ZT pin, T<sub>ZTMASK</sub> doesn't operate QR\_ZT comparator.

- D: DC/DC OFF=>ON

- E: Same as B

- F: Same as C

- G: Count maximum frequency

- H: Because 1<sub>cycle</sub>>T<sub>zTOUT</sub>, forcibly be DC/DC OFF=>ON

#### (5-7)Soft start operations

Normally, when the power supply is turned ON, a large current flows to the AC/DC power supply. The BM1050AF builds-in a soft start function to prevent large changes in the output voltage and output current during startup.

this function is reset when the VCC pin voltage is at  $V_{UVLO2}(7.0V \text{ typ})$  or below, soft start is performed again at the next AC power-on.

During a soft start, the following post-startup operations are performed. (See turn OFF described in section 5-1) Start to 1ms -> Set to 25% when CS limiter value is normal

1ms PFC normal status -> Set to 75% when CS limiter value is normal

## (5-8)Overload protection function/Overload protection mode switching

The overload protection function monitors the overload status of the secondary output current at the FB pin, and fixes the OUT pin at low level when overload status is detected.

During overload status, current no longer flows to the photocoupler, so the QR\_FB pin voltage rises.

When this status continues for the T<sub>FOLP</sub> time (64ms typ), it is considered an over load, and the OUT pin is fixed at low level.

Once the QR\_FB pin voltage exceeds  $V_{FOLP1a}$  (2.8V typ), if it drops to lower than  $V_{FOLP1b}$  (2.6V typ) during the  $T_{FOLP}$  time (64ms typ), the overload protection timer is reset. At startup, the QR\_FB voltage is pulled up to the internal voltage by pull-up resistor, and operation starts once the voltage reaches  $V_{FOLP1a}$  (2.8V typ) or above. Therefore, the design must set the QR\_EB voltage at or below the  $V_{FOLP1b}$  (2.6V typ) voltage within the  $T_{FOLP}$  (64ms typ) time. In other words, the secondary output voltage start time must be set to within  $T_{FOLP}$  (64ms typ) after IC startup.

When an overload is detected, either auto recovery mode or latch mode can be selected for the BM1050AF. When pull-down resistance  $R_{FOLP}$  (100k $\Omega$  typ) is attached to QR\_FB pin, latch mode is set. Do not attach any  $R_{FOLP}$  value other than 100k $\Omega$ typ, since that would prevent latching due to the IC7s internal resistance ratio.

To release latching after selecting latch mode, first unplug the power supply, and then set VCC<V<sub>LATCH</sub> (typ=6.5V) to release latching.

#### (5-9)QR ZT pin OVP(Over Voltage Protection)

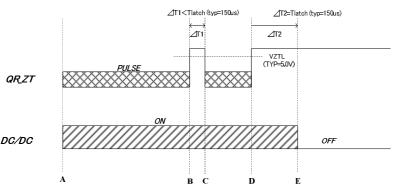

An OVP (Over Voltage Protection) function is built in for the QR\_ZT pin.

When the QR\_ZT pin voltage reaches  $V_{ZLT}$  (TYP=3.5V),over voltage status is detected. QR\_ZT pin OVP protection performed latch mode.

A mask time defined as  $T_{LATCH}$  (TYP=150us) is built in for the QR\_ZT pin OVP function. When QR\_ZT OVP status continues for 150us, overvoltage is detected. This function masks any surges (etc.) that occur at the pin. See the illustration in Figure 35. (Like VCC OVP,  $T_{LATCH}$  (TYP=150us) is built in)

Figure 35. ZTOVP and Latch mask Function

- A: DC/DC pulse operates. QR\_ZT pin operates too.

- B: QR\_ZT pin voltage> $V_{ZTL}$  (TYP=3.5V)

- C: QR\_ZT pin voltage>V<sub>ZTL</sub> (TYP=3.5V) state within  $T_{COMP}$ (typ=150us), returns to normal DC/DC operation.

- D: QR\_ZT pin voltage>V<sub>ZTL</sub> (TYP=3.5V)

- E: QR\_ZT pin voltage >  $V_{zrL}$  (TYP=3.5V) state continues  $T_{COMP}$  (typ=150us), operates latch and DC/DC OFF.

## (5-10) Quasi-resonant DC/DC block protection operation mode

Show every protection function operation mode table 6.

FB pin over load protection function is able to change AUTR/LATCH by FB pin pull down resistance.

Table 6. Protection Circuit Operation Mode of Quasi-resonant DC/DC

| ITEM       | contents                                         | LATCH/AUTOR=GND                                        |                              |                               | LATCH/AUTOR=VREF           |                                                       |                                       |                           |                            |

|------------|--------------------------------------------------|--------------------------------------------------------|------------------------------|-------------------------------|----------------------------|-------------------------------------------------------|---------------------------------------|---------------------------|----------------------------|

|            |                                                  | detection<br>method                                    | operation<br>at detection    | release<br>mothod             | operaction<br>at detection | detection<br>method                                   | operation<br>at detection             | release<br>mothod         | operaction<br>at detection |

| QR_FB_OLP1 | QR_FB pin<br>over current protection<br>function | QR_FB>2.8V state<br>continues 250ms<br>(QR_FB rising)  | DC/DC part<br>operation stop | QR_FB<2.6V<br>(QR_FB falling) | normal operation           | same as LATCH/AUTOR=GND                               |                                       |                           |                            |

| QR_FB_OLP2 | QR_FB pin<br>over current protection<br>function | QR_FB>3.6V<br>(QR_FB rising)                           | DC/DC part<br>operation stop | QR_FB<3.4V<br>(QR_FB falling) | normal operation           | same as LATCH/AUTOR=GND                               |                                       |                           |                            |

| QR_ZT OVP  | QR_ZT ipn<br>over voltage protection<br>function | QR_ZT>3.5V state<br>continue 150us<br>(QR_QR_ZTrising) | DC/DC part<br>operation stop | QR_ZT<3.5V<br>(QR_ZT falling) |                            | QR_ZT>3.5V state<br>continues 150us<br>(QR_ZT rising) | DC/DC part<br>LATCH operation<br>stop | VCC<6.5V<br>(VCC falling) | normal operation           |

## (6)Power Factor Correction Circuit (PFC: Power Factor Correction)Part

Power Factor Correction Circuit is peak current control method of fixed frequency.

It is possible to supply proper system as PFC by monitoring P\_VS pin, P\_CS pin, and P\_BO.

It is possible to control the MOSFET ON width by monitoring output voltage at P\_VS pin, AC input voltage at P\_BO pin, and MOSFET current at P\_CS pin.

The switching frequency is  $F_{PSW1}$  (typ=65kH), built in frequency hopping function (±4kHz), and contribute to low EMI. Following is detail explanation of PFC (reference figure36).

Figure 36. Diagram of PFC block

#### <u>(6-1) gm AMP</u>

P\_VS pin monitors a divide voltage between resistors of PFC output voltage. P\_VS pin is piled up ripple voltage of AC frequency (50kHz/60kHz).

The gmAMP filters this ripple voltage and controls the voltage level of P\_VSEO, by responding to error of P\_VS pin voltage P\_VS pin voltage and internal reference voltage  $V_{VSAMP}$  (typ 2.5V).

Please set cut-off frequency of filter at P\_VSEO pin showed in figure 37, to about 5~10Hz. Gm constant is designed 44[uA/V].

Figure 37. Diagram of gmAMP

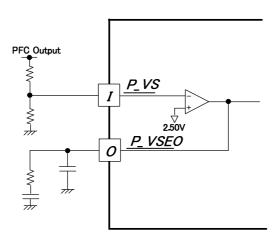

#### (6-2)Monitor of input voltage

PFC is monitored AC input voltage at the P\_BO pin.

Because the range of input voltage at P\_BO pin is  $0\sim1.8V$ , please select Rbo1 and Rbo2 to set P\_BO voltage in the range. Refer to block figure at figure 38.

Figure 38. Diagram of Input Voltage Monitor

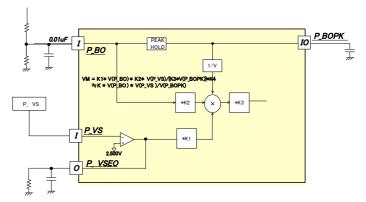

## (6-3)Maximum power limiting function

PFC maximum power is also larger as input voltage is larger.

To compensate this maximum power, PFC built-in Maximum power limiting.

Maximum power is in proportion to the square of output of multiplier V\_MULT, so it is possible to correct that maximum power depends on input voltage by dividing P\_BO voltage by P\_BOPK voltage which is peak voltage of P\_BO pin.

Figure 39. Diagram of Maximum Power Restriction Function

#### (6-4)Multiplier

A multiplier is calculated gmAMP output voltage and P\_BO pin voltage, and P\_BOPK pin voltage. Following is formula of Multiplier output.

$$V_{MULT} = \frac{K1 \times \{V(P\_BO) \times K_2 \times V(P\_VSEO)\}}{K_3 \times \{V(P\_BOPK)\}}$$

= K × V(P\_BO) × V(P\_VSEO)/ (V(P\_BOPK))

V<sub>MULT</sub>: Multiplier output voltage K: Multiplier constant

#### (6-5) Switching frequency

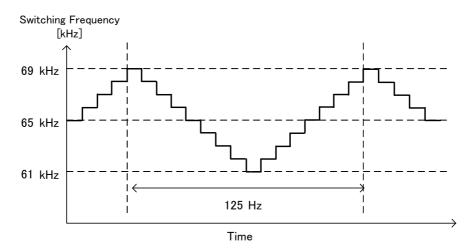

Switching frequency is averaged typ.65kHz. MAX DUTY is  $D_{MAX}$  (typ 94%), always the period has OFF width. PFC built in frequency hopping function, frequency changes every 500us. The amplitude is  $F_{PSWEL}$  (typ=±4kHz) The cycle is  $F_{PCH}$  (typ = 125Hz)( figure40).

By this function, frequency spectrums are diffused, and contribute to low EMI.

Figure 40. Frequency Hopping Function

## (6-6)LEB(Leading Edge Blanking) function

When the switching MOSFET is turned ON, surge current occurs at each capacitor charge /discharge or drive current.

For that, P\_CS voltage rise temporarily, over current limiter may be detected errors.

To prevent detection errors blanking time is built in during  $T_{\text{PLEB}}$  (typ=250ns) from P\_OUT pin changing L  $\rightarrow$ H..

This blanking function enables a reduction of  $\ensuremath{\mathsf{P}\_CS}$  pin noise filter.

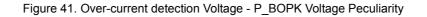

#### (6-7) Over current protection function

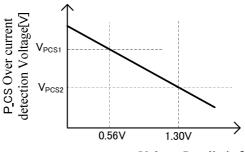

P\_CS pin built in over current protection function for MOSFET. This function operates in pulse by pulse, and detects over current. Over current detection voltage is changed by P\_BOPK pin voltage. Over current detection voltage is  $V_{PCS1}$  (typ = 1.16V) at P\_BOPK voltage = 0.56V,  $V_{PCS2}$  (typ = 0.60V) at P\_BOPK voltage = 1.30V.

Show figure41 changing of over current detection voltage by P\_BOPK pin voltage.

Over-current detection value  $I_{PCS}$  is decided  $I_{PCS}=V_{PCS}/R_s$  by external resistance  $R_s$  at figure 42.

P\_BOPK pin Voltage Peculiarity[V]

Figure 42. Diagram of Over current Protection

## (6-8)P VS short protection function

PFC built in short protection function at P\_VS. Switching is stopped at P\_VS voltage<V<sub>P\_SHORT</sub> (0.30Vtyp).

## (6-9) Gain increase function in P VS low voltage

Dropping output voltage by suddenly load change, because PFC voltage response is slow, output voltage is low for a long time. Therefore, PFC is speed up voltage control loop gain when P\_VS pin voltage is low up to  $V_{PGUP}(typ = 2.25V)$ (Output voltage - 10%). In the operation, ON-duty at P\_OUT pin increases, PFC prevents from output voltage dropping for a long time. This operation is stopped when P\_VS pin voltage is upper than  $V_{GUP}(typ=2.25V)$ .

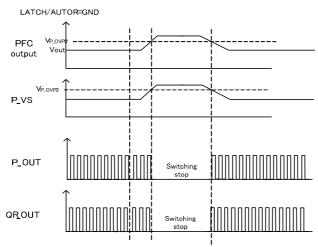

#### (6-10)P VS first over voltage protection function

#### (6-11)P VS second over voltage protection function

PFC built in second over voltage protection, for the case that P\_VS voltage exceeds over first over voltage protection voltage  $V_{P_{-}OVP1}$ . It is possible to switch Latch protection (LATCH/AUTOR=H) or auto recovery (LATCH/AUTOR=L) by LATCH/AUTOR pin. In case of latch operation, P\_VS pin voltage exceeds  $V_{P_{-}OVP2}$  (typ=2.725V)(output voltage pulse9%) during  $T_{P_{-}OVP2a}$  (Typ=32ms), PFC switching is stopped.

In case of auto recovery, P\_VS pin voltage is exceeded  $V_{P_{-}OVP2}$  (typ=2.725V), switching is stopped instantly. When P\_VS pin voltage decrease lower than  $V_{P_{-}OVP2}$  (typ=2.725V), switching operation is re-start. Refer to figure44.

Figure 44. VS Second Over Voltage Protection (at auto recovery mode)

Figure 45. Operation of P\_VS Second Over Voltage Protection (at latch mode)

Switching is stopped by second over voltage protection in the case that the P\_VS pin loop of output voltage is open loop.

# BM1050AF-G

### (6-12)PFC burst operation

PFC built-in burst operation for preventing PFC output voltage from rising at light load.

This function is that PFC monitors P\_VSEO pin at light load, switched burst operation or not.

Burst operation voltage depends on P\_BOPK voltage.

In case of P\_BOPK voltage = 0.56V, burst function operates when P\_VSEO voltage is lower than

VSEO=V<sub>P\_BURST</sub> (0.266V typ). In case of P\_BOPK voltage = 1.30V, burst function operates when P\_VSEO voltage is lower than VSEO=V<sub>P\_BURST</sub> (0.128V typ)

Refer to the change of burst voltage for P\_BOPK voltage figure46.

Figure 46. Diagram of P\_VSEO burst voltage by P\_BOPK voltage

#### (6-13) Operation mode of PFC block protection

Show operation mode every protection function at Table7.

#### Table 7. Protection Circuit Operation mode of PFC

| ITEM                     | contents                                            | LATCH/AUTOR=GND              |                            |                               |                            | LATCH/AUTOR=VREF        |                           |                   |                            |

|--------------------------|-----------------------------------------------------|------------------------------|----------------------------|-------------------------------|----------------------------|-------------------------|---------------------------|-------------------|----------------------------|

|                          |                                                     | detection<br>method          | operation<br>at detection  | release<br>mothod             | operaction<br>at detection | detection<br>method     | operation<br>at detection | release<br>mothod | operaction<br>at detection |

| P_VS SHORT<br>PROTECTION | P_VS PIN<br>short protection function               | P_VS<0.30V<br>(P_VS falling) | PFC部<br>operation stop     | P_VS>0.30V<br>(P_VS rising)   | normal operation           | Same as LATCH/AUTOR=GND |                           |                   |                            |