# JEDEC STANDARD

Thermal Impedance Measurements for Vertical Power MOSFETs (Delta Source-Drain Voltage Method)

**JESD24-3**

NOVEMBER 1990 (Reaffirmed: OCTOBER 2002)

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

#### NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or call (703) 907-7559 or www.jedec.org

Published by

©JEDEC Solid State Technology Association 2003

2500 Wilson Boulevard

Arlington, VA 22201-3834

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

PRICE: Please refer to the current

Catalog of JEDEC Engineering Standards and Publications or call Global Engineering

Documents, USA and Canada 1-800-854-7179, International (303) 397-7956

Printed in the U.S.A. All rights reserved

# PLEASE!

DON'T VIOLATE THE LAW!

This document is copyrighted by JEDEC and may not be reproduced without permission.

Organizations may obtain permission to reproduce a limited number of copies through entering into a license agreement. For information, contact:

JEDEC Solid State Technology Association 2500 Wilson Boulevard Arlington, Virginia 22201-3834 or call (703) 907-7559

# THERMAL IMPEDANCE MEASUREMENTS FOR

# VERTICAL POWER MOSFETS (DELTA SOURCE-DRAIN VOLTAGE METHOD)

# CONTENTS

| Section                                                                                                        | <u>Page</u> |

|----------------------------------------------------------------------------------------------------------------|-------------|

| <ol> <li>Purpose</li> <li>Definitions</li> </ol>                                                               | 1<br>2      |

| 3. Apparatus 3.1 Thermocouple                                                                                  | 3           |

| <ul><li>3.2 Temperature</li><li>3.3 K-Factor Calibration Setup</li><li>3.4 Test Circuit</li></ul>              | 3<br>3<br>4 |

| 3.5 Measurement of Source-Drain Forward Voltage                                                                | 6           |

| 4. Measurement of the Temperature Sensitive Parameter 4.1 Calibration                                          | 6<br>7      |

| 5. Test Procedure 5.1 Calibration 5.2 Reference Point Temperature                                              | 8<br>8<br>8 |

| 5.2 Reference Format Temperature 5.3 Thermal Measurements 5.4 Value of Thermal Impedance                       | 8<br>9      |

| 6. Test Conditions and Measurements to be Specified and Recorded                                               | 10          |

| 6.1 K-Factor Calibration                                                                                       | 10          |

| <ul> <li>6.2 Thermal Impedance Measurements</li> <li>6.3 _V<sub>DS</sub> Measurements for Screening</li> </ul> | 11<br>12    |

# THERMAL IMPEDANCE MEASUREMENTS FOR VERTICAL POWER MOSFETS (DELTA SOURCE-DRAIN VOLTAGE METHOD)

(From JEDEC Council Ballot JCB-90-03, formulated under the cognizance of JC-25 Committee on Transistors and Intelligent Power Devices.)

#### 1. PURPOSE

The purpose of this test method is to measure the thermal impedance of the MOSFET under the specified conditions of applied voltage, current and pulse duration. The temperature sensitivity of the forward voltage drop of the source-drain diode is used as the junction temperature indicator. This method is particularly suitable to enhancement mode, power MOSFETs having relatively long thermal response times. This test method may be used to measure the thermal response of the junction to a heating pulse, to ensure proper die mountdown to its case, or the dc thermal resistance, by the proper choice of the pulse duration and magnitude of the heating pulse. The appropriate test conditions and limits are detailed in Section 6.

# 2. DEFINITIONS

The following symbols and terms shall apply for the purpose of this test method:

- (a)  $I_{M}$  Current in the source-drain diode during measurement of the source-drain voltage.

- (b) I, Heating current through the drain.

- (c)  $V_{\rm H}$  Heating voltage between the drain and source.

- (d)  $P_H$  Magnitude of the heating power pulse applied to DUT in watts; the product of  $I_H$  and  $V_H$ .

- (e)  $t_{H}$  Heating time during which  $P_{H}$  is applied.

- (f)  $\alpha_{SD}$  Voltage-temperature coefficient of  $V_{SD}$  with respect to  $T_{J}$ ; in mV/°C.

- (g) K Thermal calibration factor equal to reciprocal of  $\alpha_{\rm SD}$ ; in  $^{\circ}{\rm C/mV}$ .

- (h) T<sub>J</sub> Junction temperature in degrees Celsius.

#### 2. DEFINITIONS (Continued)

- $T_{Ji}$  Junction temperature in degrees Celsius before start of the power pulse.

- T<sub>Jf</sub> Junction temperature in degrees Celsius at the end of the power pulse.

- (i)  $T_{x}$  Reference temperature in degrees Celsius.

- $T_{x_i}$  Initial reference temperature in degrees Celsius.

- $T_{xf}$  Final reference temperature in degrees Celsius.

- (j) V<sub>sp</sub> Source-drain diode voltage drop in millivolts.

- $V_{\text{SD}i}$  Initial source-drain voltage drop in millivolts.

- $V_{\text{SDf}}$  Final source-drain voltage drop in millivolts.

- (k)  $t_{MD}$  Measurement delay time is defined as the time from the removal of heating power  $P_{H}$  to the start of the  $V_{SD}$  measurement.

- (1)  $t_{SW}$  Sample window time during which final  $V_{SD}$  measurement is made.

- (m)  $V_{GS(M)}$  Gate-source voltage applied during the initial and final measurement periods.

- (n)  $Z_{\theta JX}$  Transient junction-to-reference point thermal impedance in degrees Celsius/Watt.  $Z\theta_{JX}$  for specified power pulse duration is:

$$Z_{eJX} = (T_{Jf} - T_{Ji} - \hat{T}_{X}) / P_{H}$$

where \_\_T\_x = change in reference point temperature during the heating pulse (see Sections 5.2 and 5.4). For short heating pulses, e.g., die attach evaluation, this term is normally negligible.)

#### 3. APPARATUS

The apparatus required for this test shall include the following as applicable to the specified test procedure.

# 3.1 Thermocouple

A thermocouple for measuring the case temperature at a specified point. The recommended reference point shall be located on the case under the heat source. Thermocouple material shall be copperconstantan (Type T) or equivalent. The wire size shall be no larger than AWG size 30. The junction of the thermocouple shall be welded to form a bead rather than soldered or twisted. The accuracy of the thermocouple and its associated measuring system shall be  $\pm$  0.5°C. Proper mounting of the thermocouple to ensure intimate contact to the reference point is critical for system accuracy.

#### 3.2 Temperature

A controlled temperature environment capable of maintaining the case temperature during the device calibration procedure to within  $\pm~1^{\circ}\text{C}$  over the temperature range of 23°C to 100°C, the recommended temperature for measuring K-factor.

#### 3.3 K-Factor Calibration Setup

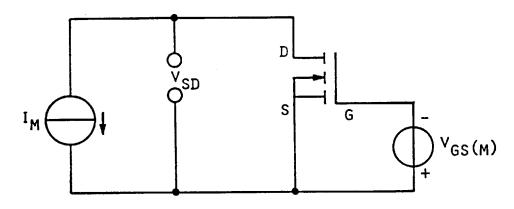

A K-factor calibration setup is shown in Figure 1 that measures  $\rm V_{SD}$  for a specified value of  $\rm I_M$  in an environment in which temperature is both controlled and measured. A temperature-controlled, circulating fluid bath is recommended. The current source must be capable of supplying  $\rm I_M$  with an accuracy of  $\pm$  1%. The voltage source must be capable of supplying  $\rm V_{GS(M)}$  with an accuracy of  $\pm$  1%. This voltage is applied in such a way as to turn the DUT off (i.e., — gate negative with respect to source for n-channel device). The voltage measurement of  $\rm V_{SD}$  shall be made using Kelvin contacts and with voltmeters capable of 1 mV resolution. The device-to-current source wire size shall be sufficient to handle the measurement current (AWG size 22 stranded is typically used for up to 100 mA).

Figure 1 K-Factor Calibration Setup

#### 3.4 Test Circuit

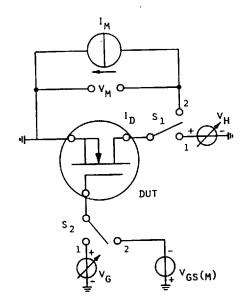

A test circuit used to control the device and to measure the temperature using forward voltage of the source-drain diode as the temperature sensing parameter is shown in Figure 2. Polarities shown are for n-channel devices, but the circuit may be used for p-channel types by reversing the polarities of the voltage and current sources.

Figure 2

Thermal Impedance Measurement Circuit

(Source-Drain Diode Method)

#### 3.4 Test Circuit (Continued)

The circuit consists of the DUT, three voltage sources, a current source, and two electronic switches. During the heating phase of the measurement, switches S1 and S2 are in position 1. The values of  $V_{\text{G}}$  and  $V_{\text{H}}$  are adjusted to achieve the desired values of  $I_{\text{D}}$  and  $V_{\text{DS}}$  for the  $P_{\text{H}}$  "heating" condition.

To measure the initial and post heating pulse junction temperatures of the DUT, switches S1 and S2 are each switched to position 2. This puts the gate at the measurement voltage level  $V_{\text{GS(M)}}$  and connects the current source  $I_{\text{M}}$  to supply forward measurement current to the source-drain diode. The polarity of the current source is such that the voltage applied to the MOSFET source and drain are opposite to those employed during normal MOSFET operation.

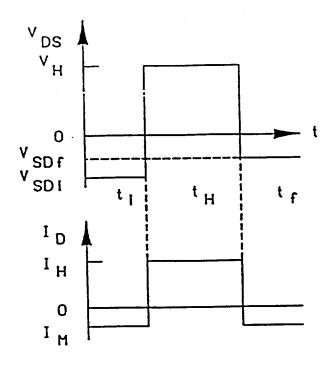

Figures 3 and 4 show the waveforms associated with the three segments of the test.

Figure 3

Device Waveforms During the Three Segments

of the Thermal Test

#### 3.4 Test Circuit (Continued)

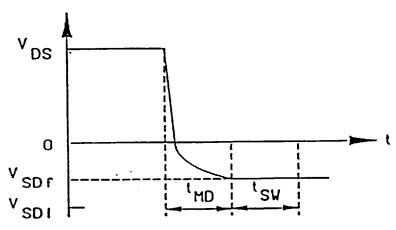

The value of  $t_{MD}$  is critical to the accuracy of the measurement and must be properly specified in order to ensure measurement repeatability. Note that some test equipment manufacturers include the sample and hold window time  $t_{SV}$  within their  $t_{MD}$  specification.

Figure 4 Second  $V_{so}$  Measurement Waveform

# 3.5 Measurement of Source-Drain Forward Voltage

Suitable sample-and-hold voltmeter or oscilloscope to measure source-drain forward voltage at specified times.  $V_{SD}$  shall be measured to within 5 mV, or within 5% of  $(V_{SDi}-V_{SDf})$ , whichever is less.

# 4. MEASUREMENT OF THE TEMPERATURE SENSITIVE PARAMETER

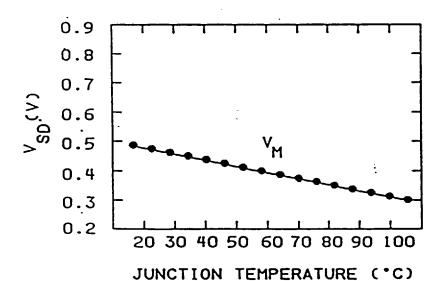

The required calibration of  $V_{SD}$  vs  $T_j$  is accomplished by monitoring  $V_{SD}$  for the required value of  $I_M$  as the heat sink temperature (and thus the DUT temperature) is varied by external heating. The magnitude of  $I_M$  shall be chosen so that  $V_{SD}$  is a linearly decreasing function over the expected range of  $T_j$  during the power pulse.  $I_M$  must be large enough to ensure that the source-drain junction is turned on, but not so large as to cause any significant self-heating. (This will normally be 10 mA for small power devices and up to 100 mA for large ones.) The  $V_{GS(M)}$  value must be large enough to decouple the gate from controlling the DUT; typical values are in the 1 to 5 V range. An example calibration curve is shown in Figure 5.

#### 4.1 Calibration

When screening to ensure proper die attachment within a given lot or in a group of the same type number devices of one manufacturer, this calibration step is not required. In such cases, the measure of the thermal response may be delta  $V_{\text{SD}}$  for a short heating pulse, and the computation of  $\hat{T}_{\text{I}}$  or  $Z_{\text{eJX}}$  is not necessary. (For this purpose,  $t_{\text{N}}$  shall be 10 ms for TO-39 size packages and 100 ms for TO-3 packages.)

A calibration factor K (which is the reciprocal of  $\alpha_{\text{SD}}$  or the slope of the curve in Figure 5) can be defined as

$$K = -\frac{1}{\alpha_{SD}} = \begin{vmatrix} T_{J1} - T_{J2} \\ -\frac{1}{2} - \frac{1}{2} - \frac{1}{2} \end{vmatrix} \circ_{C/mV}$$

Figure 5 Example Curve of  $V_{SD}$  vs  $T_J$

#### 4.1 Calibration (Continued)

It has been found that experimentally that the K-factor variation for all devices within a given device type class is small. The usual procedure is to perform a K-factor calibration on a 10 to 12 piece sample from a device lot and determine the average K and standard deviation ( $\tilde{o}$ ). If  $\tilde{o}$  is less than or equal to 3% of the average value of K, then the average value of K can be used for all devices within the lot. If  $\tilde{o}$  is greater than 3% of the average value of K, then all the devices in the lot shall be calibrated and the individual values of K shall be used in thermal impedance calculations or in correcting  $\hat{v}_{SD}$  values for comparison purposes.

#### 5. TEST PROCEDURE

#### 5.1 Calibration

K-factor must be determined according to the procedure outlined in Section 4, except as noted in 4.1.

# 5.2 Reference Point Temperature

The reference point is usually chosen to be on the bottom of the transistor case directly below the semiconductor chip in a TO-204 metal can or in closer proximity to the chip in other styles of packages. Reference temperature point location must be specified and its temperature shall be monitored using the thermocouple mentioned in paragraph 3.1 during the preliminary testing. If it is ascertained that  $T_{\chi}$  increases by more than 5% of the measured junction temperature rise during the power pulse, then either the heating power pulse magnitude must be decreased, the DUT must be mounted in a temperature-controlled heat sink, or the calculated value of thermal impedance must be corrected to take into account the thermal impedance of the reference point to the cooling medium or heat sink.

Temperature measurements for monitoring, controlling and/or correcting for reference point temperature changes are not required if the  $t_{\rm H}$  value is low enough to ensure that the heat generated within the DUT has not had time to propagate through the package. Typical values of  $t_{\rm H}$  for this case are in the 10 ms to 500 ms range, depending on DUT package type and material.

# 5.3 Thermal Measurements

The following sequence of tests and measurements must be made.

#### 5.3.1 Prior to the Power Pulse

- (a) Establish reference point temperature Txi.

- (b) Apply measurement current Im.

- (c) Apply gate-source measurement voltage  $V_{GS(M)}$ .

- (d) Measure source-drain voltage drop  $V_{\text{SD}}$ ; (a measurement of the initial junction temperature).

#### 5.3.2 Heating Pulse Parameters

- (a) Apply drain-source heating voltage V<sub>u</sub>.

- (b) Apply drain heating current  $I_{\rm H}$  as required by adjustment of gate-source voltage.

- (c) Allow heating condition to exist for the required heating pulse duration  $t_{\mu}$ .

- (d) Measure reference point temperature  $T_{\chi_f}$  at the end of heating pulse duration.

NOTE:  $T_{\chi}$  measurement are not required if the  $t_{H}$  value meets the requirements stated in Section 5.2.

#### 5.3.3 Post Power Pulse Measurements

- (a) Apply measurement current I<sub>M</sub>.

- (b) Apply gate-source measurement voltage  $V_{GS(M)}$ .

- (c) Measure source-drain voltage drop  $V_{\text{SDf}}$  (a measurement of the final junction temperature).

- (d) Time delay between the end of the power pulse and the completion of the  $V_{\rm SDf}$  measurement as defined by the waveform of Figure 4 of MIL-SPEC-3161 in terms of  $t_{\rm MD}$  plus  $t_{\rm SW}$ .

# 5.4 Value of Thermal Impedance

The value of thermal impedance,  $\mathbf{Z}_{\text{eJX}}$ , is calculated from the following formula:

$$Z_{\text{eJX}} = \hat{\underline{}} T_{\text{J}}/P_{\text{H}}$$

$$= \begin{vmatrix} K & (V_{\text{SDf}} - V_{\text{SDi}}) \\ ------- & (I_{\text{H}}) & (V_{\text{H}}) \end{vmatrix} \circ C/W$$

# 5.4 Value of Thermal Impedance (Continued)

This value of thermal impedance will have to be corrected if  $T_{\chi f}$  is greater than  $T_{\chi i}$  by 5°C. The correction consists of subtracting out the component of thermal impedance to the thermal impedance from the reference point (typically the device case) to the cooling medium or heat sink.  $T_{\chi}$  measurements are not required if the  $t_{\mu}$  value meets the requirements stated in Section 5.2.

This thermal impedance component has a value calculated as follows:

$$Z_{\Theta X-HS} = \hat{\underline{}} T_X/P_H$$

$$= (T_{Xf} - T_{Xi}) / [(I_H) (V_H)]$$

where

HS = Cooling medium or heat sink (if used)

then  $Z_{e,ix} \mid = Z_{e,ix} \mid - Z_{ex-HS}$

Corrected Calculated

Note that this last step is not necessary for die attach evaluation (see Section 4.1).

#### 6. TEST CONDITIONS AND MEASUREMENTS TO BE SPECIFIED AND RECORDED

#### 6.1 K-Factor Calibration

6.1.1 Test Conditions to be Specified

| (a)  | I <sub>M</sub>     | Current magnitude (See Detail Specification for current value)  | <br>mA   |

|------|--------------------|-----------------------------------------------------------------|----------|

| (b)  | V <sub>GS(M)</sub> | Gate-source voltage (Normally in the range of 0 to -0.6 V.)     | <br>_ v  |

| (c)  |                    | Initial junction temperature (Normally 25 $\pm$ 5°C)            | <br>- °C |

| (d)  |                    | Final junction temperature (Normally 100 $\pm$ 10 $^{\circ}$ C) | <br>. °C |

| 6.1. | 2 Rec              | ord the Following Data                                          |          |

| (a)  |                    | Initial V <sub>SD</sub> voltage                                 | <br>mV   |

| (b)  |                    | Final V <sub>sD</sub> voltage                                   | <br>mV   |

#### 6.1.3 K-Factor Calculation

The K-factor should be calculated per the following equation:

$$K = \begin{vmatrix} T_{J1} - T_{J2} \\ - - - - - - - - - - - - - \\ V_{SD1} - V_{SD2} \end{vmatrix} \circ_{C/mV}$$

# 6.1.4 Die Attachment Evaluation

For die attachment evaluation, this step may not be necessary (see paragraph 4.1.).

# 6.2 Thermal Impedance Measurements

The following conditions should be specified:

| (a)   | I <sub>M</sub>             | Measuring current (Must be the same as used for K-factor calibration)                               | ιA |

|-------|----------------------------|-----------------------------------------------------------------------------------------------------|----|

| (b)   | V <sub>GS(M)</sub>         | Gate-source voltage (Must be the same as used for K-factor calibration)                             | V  |

| (c)   | IH                         | Drain heating current                                                                               | Α  |

| (d)   | $v_{\scriptscriptstyle H}$ | Drain-source heating voltage                                                                        | v  |

| (e)   | t <sub>H</sub>             | Heating time                                                                                        | s  |

| (f)   | t <sub>MD</sub>            | Measurement time delay µ                                                                            | ιs |

| (g)   | t <sub>sw</sub>            | Sample window time µ                                                                                | ιs |

|       |                            | $I_{H}$ and $V_{H}$ are usually chosen so that $P_{H}$ is approximatelyice rated power dissipation. | У  |

| 6.2.2 | Reco                       | ord the Following Data                                                                              |    |

| (a)   | Txi                        | Initial reference temperature                                                                       | °C |

| (b)   | $\mathbf{T}_{Xf}$          | Final reference temperature                                                                         | °C |

| 6.2.2 | 2.1 _1                     | J <sub>SD</sub> Data                                                                                |    |

| (a)   |                            |                                                                                                     | nV |

|       |                            |                                                                                                     |    |

| Addendum No. 4 Page 12                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2.2.2 V <sub>SD</sub> Data                                                                                                                    |

| (a) V <sub>SD(i)</sub> Initial source-drain voltage V                                                                                           |

| (b) V <sub>SD(f)</sub> Final source-drain voltage                                                                                               |

| $T_{\chi}$ measurements are not required if the $t_{\text{H}}$ value meets the requirements stated in Section 5.2.                              |

| 6.2.3 Thermal Impedance Calculation                                                                                                             |

| Calculate thermal impedance using the procedure and equation shown in Section 5.4.                                                              |

| 6.3 _VDS Measurements for Screening                                                                                                             |

| These measurements are made for $t_{\rm H}$ values that meet the intent of Section 4.1 and the requirements stated in Section 5.2.              |

| 6.3.1 Conditions to be Specified                                                                                                                |

| (a) I <sub>M</sub> Measuring current m                                                                                                          |

| (b) V <sub>GS(M)</sub> gate-source voltage                                                                                                      |

| (c) I <sub>H</sub> Drain heating current P                                                                                                      |

| (d) V <sub>H</sub> Drain-source heating voltage                                                                                                 |

| (e) t <sub>H</sub> Heating time                                                                                                                 |

| (f) $t_{MD}$ Measurement time delay $\mu$ s                                                                                                     |

| (g) $t_{SW}$ Sample window time $\mu_{SW}$                                                                                                      |

| The values of $I_{\text{H}}$ and $V_{\text{H}}$ are usually chosen equal to or greater than the values used for thermal impedance measurements. |

| 6.3.2 Specified Limits                                                                                                                          |

| The following data is compared to the specified limits:                                                                                         |

| 6.3.2.1 <u>^</u> V <sub>SD</sub> Data                                                                                                           |

| (a)                                                                                                                                             |

JEDEC Standard No. 24-3

| 6.3 | .2.2 V <sub>s</sub> | <sub>SD</sub> Data           |   |    |

|-----|---------------------|------------------------------|---|----|

| (a) | V <sub>SD(i)</sub>  | Initial source-drain voltage |   | v  |

| (b) | V <sub>SD(f)</sub>  | Final source-drain voltage   |   | v  |

|     |                     | Compute _V <sub>SD</sub>     | r | nV |

# 6.3.2.3 Optional Calculation

Optionally calculate  $\hat{T}_J$  for comparison and/or screening purposes if the K-factor results (see Sections 4. and 6.1) produce a  $\tilde{o}$  greater than 3% of the average value of K.

$\hat{T}_{J} = K(\hat{V}_{SD}) \, ^{\circ}C.$