**RT9718**

过压保护芯片:RT9718BGQW 联系人: 王先生 18129930080

# **Over Voltage Protection IC**

### **General Description**

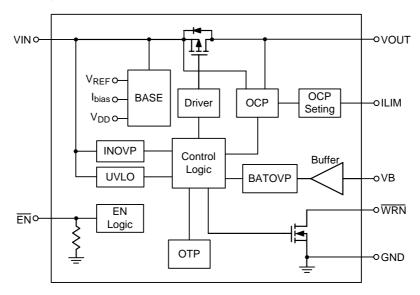

The RT9718 is an integrated circuit optimized to protect low voltage system from abnormal high input voltage (up to 28V). The IC monitors the input voltage, battery voltage and the charging current to make sure all three parameters are operated in normal range. When the input voltage exceeds a certain OVP threshold voltage level, the IC will turn off the power MOSFET within 1µs to remove the power before any damage occurs. The RT9718 also can provide a voltage output without the existence of battery.

The current in the power MOSFET is also limited to prevent charging the battery with an excessive current. The current limit can be programmed by an external resistor between ILIM and GND. The OCP function also has a 4-bit binary counter that accumulates during an OCP event. When the total count reaches consecutive 16 times, the power MOSFET is turned off permanently unless the input power is recycled.

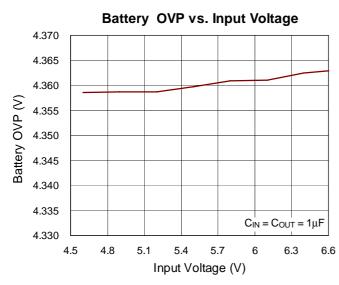

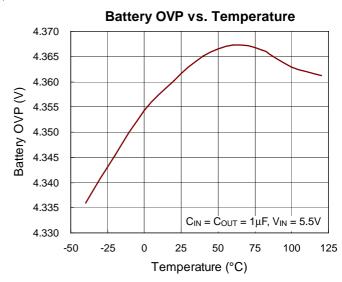

The IC also monitors the battery voltage, Once the battery voltage exceeds 4.35V and last for more then 180us blinking time, the RT9718 will turn off the MOSFET. The internal logic control will turn off the power MOSFET permanently when the battery over-voltage event occurs for consecutive 16 times.

# **Ordering Information**

RT9718 🔲 🔲 📮 Package Type QW: WDFN-8L 2x2 (W-Type) Lead Plating System G: Green (Halogen Free and Pb Free) Z: ECO (Ecological Element with Halogen Free and Pb free) OVP A: 6.80V B: 5.85V C: 6.25V D: 7.20V

Richtek products are:

Note:

- > RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Fully Integrated Protection Function

- Programmable OCP

- ▶ Input OVP

- Battery OVP

- Withstand High Input Voltage Up to 28V

- Over Voltage Turn Off Time Less Than 1us

- High Accuracy Protection Thresholds

- Over Temperature Protection

- High Immunity of False Triggering Under Transients

- Warning Indication Output

- Enable Input

- Thermal Enhanced WDFN Package

- RoHS Compliant and Halogen Free

### **Applications**

- Cellular Phones

- Digital Cameras

- PDAs and Smart Phones

- Portable Instruments

# **Pin Configurations**

(TOP VIEW)

WDFN-8L 2x2

# **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

DS9718-02 May 2011 www.richtek.com

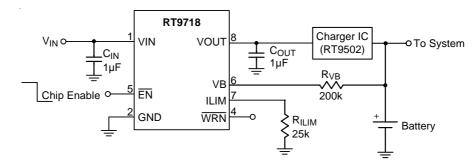

# **Typical Application Circuit**

# **Functional Pin Description**

| Pin No.        | Pin Name | Pin Function                                                                             |

|----------------|----------|------------------------------------------------------------------------------------------|

| 1              | VIN      | The input power source. The VIN can withstand up to 28V input.                           |

| 2              | GND      | Analog Ground.                                                                           |

| 3              | NC       | No Internal Connection.                                                                  |

| 4              | WRN      | This is an open-drain logic output that turns LOW when any protection event occurs.      |

| _              | EN       | Chip Enable (Active Low). Pull this pin to low or leave it floating to enable the IC and |

| 5              |          | force it to high to disable the IC.                                                      |

| 6              | VB       | Battery voltage monitoring input. This pin is connected to the battery pack positive     |

| 0              |          | terminal via an isolation resistor.                                                      |

| 7              | ILIM     | Over current protection threshold setting pin. Connect a resistor between this pin       |

| /              |          | and GND to set the OCP threshold.                                                        |

| 8              | VOUT     | Output through the power MOSFET.                                                         |

| 0 (Eyposo Bod) | GND      | The exposed pad must be soldered to a large PCB and connected to GND for                 |

| 9 (Expose Pad) |          | maximum thermal dissipation.                                                             |

# **Function Block Diagram**

联系人: 王先生 18129930080

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>IN</sub>                                     | -0.3V to 28V   |

|-----------------------------------------------------------------------------|----------------|

| • VOUT, VB                                                                  | -0.3V to 7V    |

| • Other Pins                                                                | -0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WDFN-8L 2x2                                                                 | - 0.606W       |

| Package Thermal Resistance (Note 2)                                         |                |

| WDFN-8L 2x2, $\theta_{JA}$                                                  | - 165°C/W      |

| WDFN-8L 2x2, $\theta_{JC}$                                                  | - 20°C/W       |

| • Junction Temperature                                                      | - 150°C        |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C        |

| Storage Temperature Range                                                   | -65°C to 150°C |

| • ESD Susceptibility (Note 3)                                               |                |

| HBM (Human Body Mode)                                                       | · 2kV          |

| MM (Machine Mode)                                                           | - 200V         |

| December and Operating Conditions (1)                                       |                |

### **Recommended Operating Conditions** (Note 4)

## **Electrical Characteristics**

( $V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                   |                                 | Symbol                                | Test Conditions                          | Min  | Тур  | Max  | Unit |

|-----------------------------|---------------------------------|---------------------------------------|------------------------------------------|------|------|------|------|

| Power On Reset              |                                 |                                       |                                          |      |      |      |      |

|                             | RT9718A                         |                                       |                                          | 4    |      | 6.5  |      |

| 0                           | RT9718B                         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                                          | 4    |      | 5.5  | V    |

| Operation Voltage           | RT9718C                         | Vin                                   |                                          | 4    |      | 5.9  | V    |

|                             | RT9718D                         |                                       |                                          | 4    |      | 6.9  |      |

| Supply Voltage POR          | Threshold                       | VPOR                                  | V <sub>POR</sub> Rising                  | 2.5  | 2.7  | 2.9  | V    |

| Deglitch Time of PO         | R                               |                                       |                                          |      | 8    |      | ms   |

| Under Voltage Locko         | Under Voltage Lockout Threshold |                                       | V <sub>UVLO</sub> Falling                | 2.45 |      | 2.75 | V    |

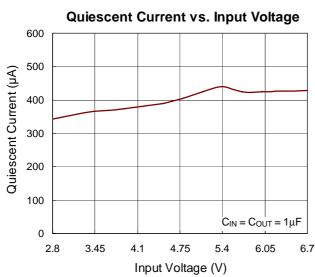

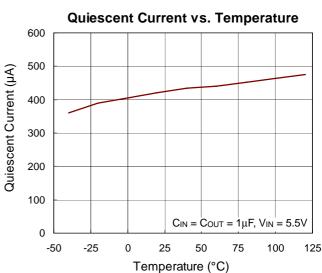

| Input Quiescent Current     |                                 | IQ                                    | <del>EN</del> = 0V                       |      | 500  | 600  | μА   |

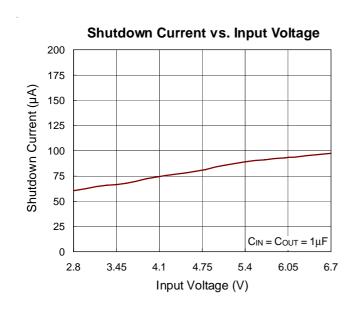

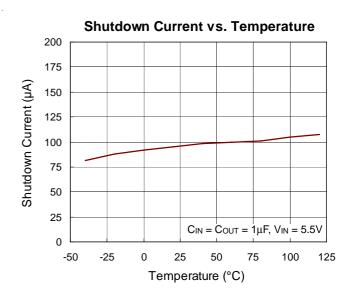

| Input Shutdown Current      |                                 | I <sub>SHDN</sub>                     | <del>EN</del> = 5V                       |      | 65   | 95   |      |

| Protections                 |                                 |                                       |                                          |      |      |      |      |

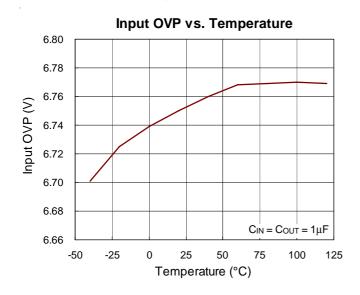

|                             | RT9718A                         |                                       |                                          | 6.6  | 6.8  | 7    |      |

| Input OVP                   | RT9718B                         | \/                                    |                                          | 5.6  | 5.85 | 6    | \/   |

| Threshold Voltage           | RT9718C                         | V <sub>IN_OVP</sub>                   |                                          | 6.05 | 6.25 | 6.45 | V    |

|                             | RT9718D                         |                                       |                                          | 7    | 7.2  | 7.4  |      |

| Input OVP Hysteresis        |                                 |                                       |                                          |      | 60   | 100  | mV   |

| Input OVP Propagation Delay |                                 |                                       | V <sub>OUT</sub> = V <sub>IN</sub> x 80% |      |      | 1    | μS   |

| Input OVP Recovery Delay    |                                 |                                       |                                          |      | 8    |      | ms   |

To be continued

DS9718-02 May 2011 www.richtek.com

# **RT9718**

RICHTEK

| Parameter                             |            | Symbol            | Test Conditions                                         | Min   | Тур  | Max  | Unit     |

|---------------------------------------|------------|-------------------|---------------------------------------------------------|-------|------|------|----------|

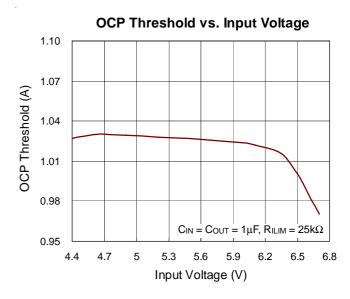

| Over Current Protection               |            | I <sub>OCP</sub>  | As R <sub>ILIM</sub> = 25k                              | 0.93  | 1    | 1.07 | Α        |

| Over Current Protection Blanking Time |            | T <sub>OC</sub>   |                                                         |       | 180  |      | μS       |

| Over Current Recover D                | Delay      |                   |                                                         |       | 64   |      | ms       |

| Battery Over Voltage Protection       |            | VB <sub>OVP</sub> | Threshold Rising                                        | 4.3   | 4.35 | 4.4  | V        |

|                                       |            |                   | Hysteresis                                              |       | 30   |      | mV       |

| Battery OVP Falling Thr               | eshold     |                   |                                                         | 4.225 |      |      | V        |

| Battery OVP Blanking Time             |            |                   |                                                         |       | 180  |      | μS       |

| Battery OVP Recover Delay             |            | T <sub>VBOV</sub> |                                                         |       | 8    |      | ms       |

| VB Pin Leakage Current                |            |                   | V <sub>VB</sub> = 4.4V                                  |       | 1    | 20   | nA       |

| OTP Threshold                         |            |                   | Rising                                                  |       | 140  |      | °C       |

| OTP Threshold                         |            | T <sub>SD</sub>   | Hysteresis                                              |       | 20   |      | °C       |

| OTP Recover Delay                     |            |                   |                                                         |       | 8    |      | ms       |

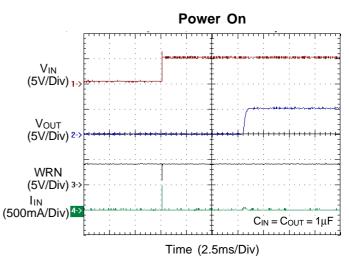

| Soft-Start Time                       |            |                   |                                                         |       | 8    |      | ms       |

| Logic                                 |            |                   |                                                         |       |      |      |          |

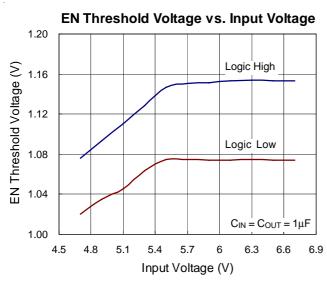

| EN Threshold Voltage                  | Logic-High | ViH               |                                                         | 1.5   |      |      | V        |

| LIN THIESHOLD VOILage                 | Logic-Low  | $V_{IL}$          |                                                         |       |      | 0.4  | V        |

| EN Internal Pull Down Resistor        |            |                   |                                                         | 100   | 200  | 400  | kΩ       |

| WRN Output Logic Low                  |            |                   | Sink 5mA                                                |       | 0.35 | 8.0  | <b>V</b> |

| WRN Output Logic High Leakage         |            |                   |                                                         |       |      | 1    | ^        |

| Current                               |            |                   |                                                         |       | -    | 1    | μΑ       |

| Power MOSFET                          |            |                   |                                                         |       |      |      |          |

| On Resistance                         |            | R <sub>ON</sub>   | I <sub>OUT</sub> = 500mA, 4.3V < V <sub>IN</sub> < 6.5V |       | 200  | 300  | mΩ       |

联系人: 王先生 18129930080

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25$ °C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. The case position of  $\theta_{JC}$  is on the exposed pad of the packages.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

联系人: 王先生 18129930080

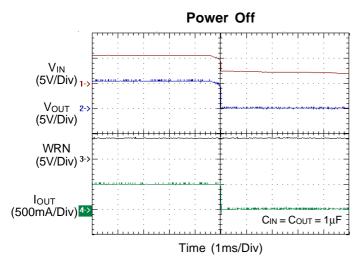

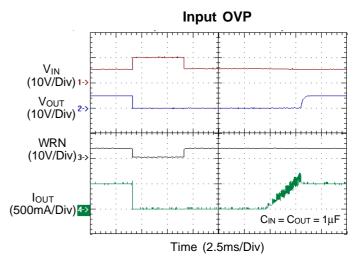

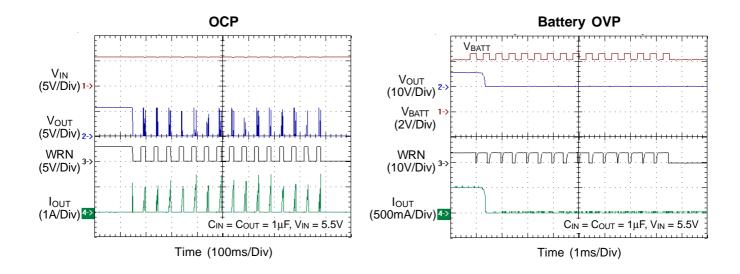

# **Typical Operating Characteristics**

DS9718-02 May 2011 www.richtek.com

DS9718-02 May 2011 www.richtek.com

## **Applications Information**

### **Power Up**

The RT9718 has a threshold of 2.7V power on reset (POR) with a built-in hysteresis of 100mV. Before the input voltage reaches the POR threshold, the RT9718 is off. When the input voltage is over the POR threshold; the RT9718 will delay for 8ms and the soft-start will be activated after the 8ms delay. The 8ms delay allows any transients at the input during a hot insertion of the power supply to settle down before the IC starts to operate.

During the soft-start transition, the RT9718 slowly turns on the internal MOSFET to reduce the inrush current.

### **Enable Control**

The RT9718 offers an enable  $(\overline{EN})$  input. When the  $\overline{EN}$  pin is pulled to logic high (>1.5V), the RT9718 will be shut down. When the  $\overline{EN}$  pin is pulled to logic low (<0.4V), the RT9718 will be powered on. The  $\overline{EN}$  pin has an internal pull-down resistor. Leaving the  $\overline{EN}$  pin floating can enable the IC.

### **Warning Indication Output**

The WRN pin is an open-drain output that indicates a LOW signal when any protection event occurs (Input OVP, Output OCP and Battery OVP). When the protection events are released and then the WRN pin indicates a HIGH signal.

### **Over Temperature Protection (OTP)**

The RT9718 monitors its own internal temperature to prevent thermal failures. The chip turns off the MOSFET when the internal temperature reaches  $140^{\circ}$ C. The IC will resume after the internal temperature is cooled down  $20^{\circ}$ C.

### Input Over Voltage Protection

The RT9718 monitors input voltage to prevent the input voltage lead to output system failures. The RT9718 input OVP threshold is set by the internal resistor. When the input voltage exceeds the threshold, the RT9718 outputs a logic signal to turn off the internal MOSFET within 1us to prevent the high input voltage from damaging the electronics in the handheld system. The hysteresis of the input OVP threshold is 100mV. When the input voltage returns to normal operation voltage rage, the RT9718 reenables the MOSFET.

### **Battery Over Voltage Protection**

The battery OVP threshold voltage is set at 4.35V in typical and the RT9718 has a built-in 180us blanking time to prevent any transient voltage from triggering the battery OVP. If the OVP situation still exists after 180us, the internal MOSFET will be turned off and the WRN pin indicates a LOW signal. The battery OVP threshold has a 30mV built-in hysteresis. The control logic contains a 4-bit binary counter. If the battery over voltage event occurs for consecutive 16 times, the MOSFET will be turned off permanently unless the input power or the enable pin is reset.

### Selecting R<sub>VB</sub>

联系人: 王先生 18129930080

The RT9718 monitors the battery voltage by the VB pin. The RT9718 will be turned off when the battery voltage exceeds the 4.35V battery OVP threshold. The VB pin is connected to the battery pack positive terminal via an isolation resistor (R<sub>VB</sub>) and the resistor is an important component. The R<sub>VB</sub> determines some parameters such as battery OVP threshold error and VB pin leakage current. Generally, it is necessary to decrease the R<sub>VB</sub> for reducing the battery OVP threshold error. However, this will increase the VB pin leakage current. So, it is an important issue to get a trade-off between the battery OVP threshold error and the VB pin leakage current. The resistance of  $200 k\Omega$  to  $1 M\Omega$  is allowed for R<sub>VB</sub>.

### **Over Current Protection (OCP)**

The RT9718 monitors the output current to prevent the output short or the charging of the battery with an excessive current. The OCP (Over Current protection) threshold can be set by the ILIM pin. The RT9718 has a built-in 180us delay time to prevent any transient noise from triggering the OCP. If the OCP situation exists for 180us, the internal MOSFET will be turned off and the WRN pin indicates a LOW signal. When the OCP happens for consecutive 16 times, the internal MOSFET will be turned off permanently unless the input power is recycled or the enable pin is toggled.

联系人: 王先生 18129930080

The OCP threshold can be set by the resistor connected between the ILIM pin and GND. The OCP threshold can be calculated by the following equation:

$$IOCP = \frac{25000}{RILIM}$$

### **Selecting Capacitors**

To get the better performance of the RT9718, it is very important to select peripherally appropriate capacitors. These capacitors determine some parameters such as input inrush current and input over shoot voltage. Generally, it is necessary to increase the input capacitance C<sub>IN</sub> for reducing the input over shoot voltage. However, this will increase the inrush current of input. There are two scenarios that can cause the input over shoot voltage. The first one is that when the AC adapter is hot-plugged and the second one is when the RT9718 has a step-down change. The cable between the AC adapter output and the handheld system input has a parasitic inductance causing the input over shoot voltage. Generally, the input over shoot voltage range is 1.5 to 2 times of the input voltage. It is recommended to use 1μF capacitance for C<sub>IN</sub> and C<sub>OUT</sub> and the rated voltage should be higher than at 1.5 to 2 times of the operation voltage.

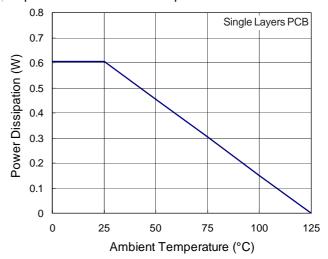

### **Thermal Considerations**

Thermal protection limits power dissipation in RT9718. When the operation junction temperature exceeds 140°C, the OTP circuit starts the thermal shutdown function and turns the pass element off. The pass elements turn on again after the junction temperature cools by 20°C.

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of RT9718, the maximum operating junction temperature is 125°C. The junction to ambient thermal resistance  $\theta_{JA}$  for WDFN-8L2x2 package is 165°C/W on the standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at T<sub>A</sub> =25°C can be calculated by following formula:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (165^{\circ}C/W) = 0.606W \text{ for WDFN}$ 8L 2x2 packages

The maximum power dissipation depends on operating ambient temperature for fixed T<sub>J(MAX)</sub> and thermal resistance  $\theta_{JA}$ . For RT9718 packages, the Figure 1 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 1. Derating Curves for RT9718 Packages

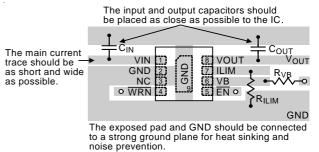

#### **Layout Consideration**

For best performance of the RT9718 series, the following guidelines must be strictly followed.

- Input and output capacitors should be placed close to the IC and connected to ground plane to reduce noise coupling.

- The GND and exposed pad should be connected to a strong ground plane for heat sink.

- Keep the main current traces as possible as short and wide.

Figure 2. PCB Layout Guide

DS9718-02 May 2011 www.richtek.com

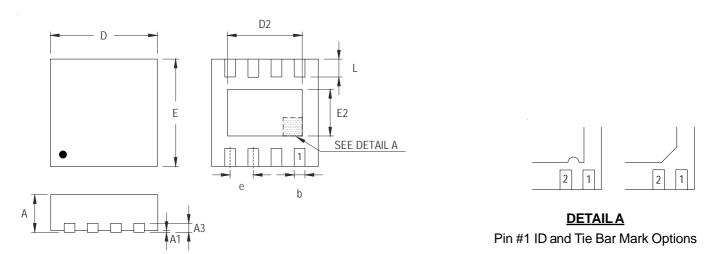

# **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| А3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D      | 1.950        | 2.050         | 0.077                | 0.081 |  |

| D2     | 1.000        | 1.250         | 0.039                | 0.049 |  |

| Е      | 1.950        | 2.050         | 0.077                | 0.081 |  |

| E2     | 0.400        | 0.650         | 0.016                | 0.026 |  |

| е      | 0.500        |               | 0.020                |       |  |

| L      | 0.300        | 0.400         | 0.012                | 0.016 |  |

W-Type 8L DFN 2x2 Package

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.

www.richtek.com DS9718-02 May 2011