# An9920A 3-Pin Switch-Mode 100mA Average Current LED Lamp Driver

#### **Features**

- Constant output average current: 100mA

- Universal 85-264VAC operation

- Fixed off-time buck converter

- Internal 475 V power MOSFET

## **Applications**

- Decorative lighting

- Low power lighting fixtures

## **General Description**

The An9920A is a pulse width modulated (PWM) high efficiency LED driver control IC. It allows efficient operation of LED strings from voltage sources ranging up to 400VDC. The An9920A includes an internal high voltage switching MOSFET controlled with fixed off-time (T<sub>OFF</sub>) of approximately 11.5 µs and average logic. The LED string is driven at constant average current, very weakly depending on the inductance value and LED quantity at wide range, thus providing constant light output and enhanced reliability. The output average current is internally fixed at 100mA. The average current control scheme provides good regulation of the output current throughout the universal AC line voltage range of 85 to 264VAC or DC input voltage of 20 to 400V and is inherently protected from input undervoltage condition.

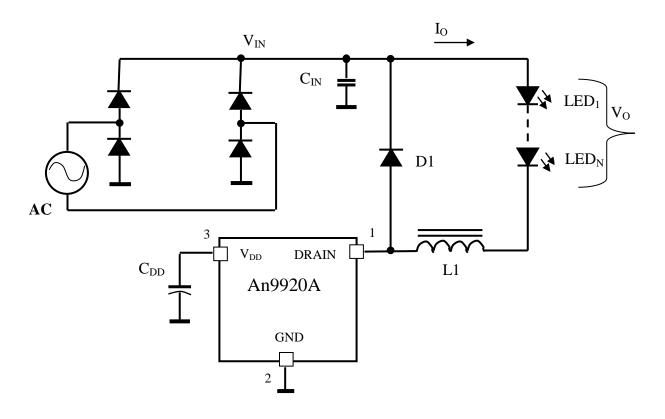

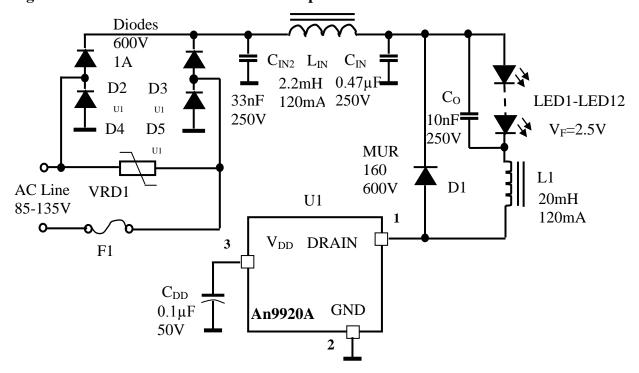

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| Parameter                            | Value              |

|--------------------------------------|--------------------|

| Supply voltage, V <sub>DD</sub>      | -0.3 to +10V       |

| Supply current, I <sub>DD</sub>      | +5mA               |

| Operating ambient temperature range  | -40 °C to +85 °C   |

| Operating junction temperature range | -40 °C to +125 °C  |

| Storage temperature range            | -65 °C to +150 °C  |

| Power dissipation @ 25 °C, SOT-89    | 1600mW (Mounted on |

|                                      | FR4 board, 25mm x  |

|                                      | 25mm x 1.57mm)     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Note 1: Also limited by package power dissipation limit, whichever is lower.

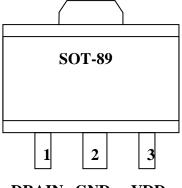

# Pin Configurations

DRAIN GND VDI

Top View

#### **Electrical Characteristics**

(Specifications are at  $T_A = 25$ °C and  $V_{DRAIN} = 50V$ , unless otherwise noted)

| Symbol                            | Description                                     | Min. | Typ. | Max. | Units | Conditions                                                                                          |  |  |  |

|-----------------------------------|-------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Regulator $(V_{DD})$              |                                                 |      |      |      |       |                                                                                                     |  |  |  |

| $V_{ m DD}$                       | V <sub>DD</sub> regulator output                | -    | 7.8  | -    | V     |                                                                                                     |  |  |  |

| $V_{DRAIN}$                       | V <sub>DRAIN</sub> supply voltage               | 20   | -    | -    | V     |                                                                                                     |  |  |  |

| $V_{UVLO}$                        | $V_{\text{DD}}$ undervoltage threshold          | 5.0  | -    | -    | V     |                                                                                                     |  |  |  |

| $\Delta V_{UVLO}$                 | $V_{\text{DD}}$ undervoltage lockout hysteresis | -    | 200  | -    | mV    |                                                                                                     |  |  |  |

| $I_{DD}$                          | Operating supply current                        | -    | 220  | 400  | μΑ    | $V_{DD(EXT)} = 8.5V, V_{DRAIN} = 40V$                                                               |  |  |  |

| Output (DRAIN)                    |                                                 |      |      |      |       |                                                                                                     |  |  |  |

| $V_{BR}$                          | Breakdown voltage *                             | 475  | -    | -    | V     |                                                                                                     |  |  |  |

| R <sub>ON</sub>                   | On-resistance                                   | -    | -    | 100  | Ω     | $I_{DRAIN} = 100 \text{mA}$                                                                         |  |  |  |

| $C_{DRAIN}$                       | Output capacitance #                            | -    | 1.0  | 5.0  | pF    | $V_{DRAIN} = 400V$                                                                                  |  |  |  |

| $I_{SAT}$                         | MOSFET saturation current #                     | 150  | 210  | -    | mA    |                                                                                                     |  |  |  |

| Current Sense Comparator          |                                                 |      |      |      |       |                                                                                                     |  |  |  |

| I <sub>TH</sub> (I <sub>O</sub> ) | Threshold average current *                     | 90   | 100  | 110  | mA    | V <sub>IN</sub> =150V, L1=33mH, Vo=60V,<br>D1-MUR160, C <sub>IN</sub> =10uF, C <sub>DD</sub> =0.1uF |  |  |  |

| $T_{BLANK}$                       | Leading edge blanking delay * #                 | 200  | 300  | 400  | ns    |                                                                                                     |  |  |  |

| $T_{ON(MIN)}$                     | Minimum on-time                                 | -    | -    | 1600 | ns    |                                                                                                     |  |  |  |

| OFF-Time Generator                |                                                 |      |      |      |       |                                                                                                     |  |  |  |

| $T_{OFF}$                         |                                                 | 8    | 11.5 | 15   | μs    |                                                                                                     |  |  |  |

#### Note:

<sup>\*-</sup> Denotes the specifications which apply over the full operating ambient temperature range of - 40 °C < T<sub>A</sub> < + 85 °C.

<sup># -</sup> Denotes guaranteed by design.

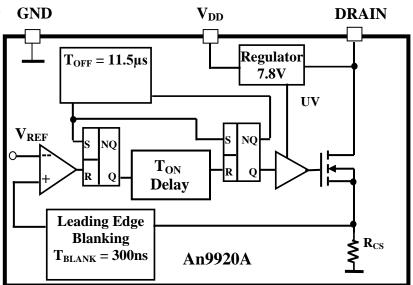

#### **Functional Description**

#### **Input Voltage Regulator**

The An9920A is a PWM average current controller for controlling a buck converter topology in continuous conduction mode (CCM). The output current is internally preset at 100mA.

When the input voltage of 20 to 400V appears at the DRAIN pin, the internal high-voltage linear regulator seeks to maintain a constant voltage 7.8VDC at the  $V_{DD}$  pin. Until this voltage exceeds the internally programmed under-voltage threshold, the output switching MOSFET is non-conductive. When the threshold is exceeded, the MOSFET turns on. The input current begins to flow into the DRAIN pin. Hysteresis is provided in the under-voltage comparator to prevent oscillation.

When the input current exceeds the internal preset average level, a current sense comparator resets a first RS flip-flop, signifying that a first  $T_{\rm ON}$  period is over, and  $T_{\rm ON}$  Delay Scheme turns on, starting another the same  $T_{\rm ON}$  period. At the end of this  $T_{\rm ON}$  period a second RS flip-flop resets, and the MOSFET turns off. At the same time, a one-shot circuit is activated that determines the duration of the off-state (11.5 $\mu$ s typ.). As soon as this time is over, the both flip-flops sets again. The new switching cycle begins.

A "blanking" delay of 300ns is provided that prevent false triggering of the current sense comparator due to the leading edge spike caused by circuit parasitics.

## **Application Information**

The An9920A is a low-cost off-line buck converter IC specifically designed for driving multi-LED strings. It can be operated from either universal AC line range of 85 to 264VAC, or 20 to 400 VDC, and drives up to tens of high brightness LEDs. All LED's can be run in series, and the An9920A regulates at constant current, yielding uniform illumination. The An9920A is compatible with triac dimmers. The output current is internally fixed at  $I_{TH}$ =100mA. This part is available in space saving TO-92 and SOT-89 package.

#### Selecting L1 and D1

There is a certain trade-off to be considered between optimal sizing of the output inductor L1 and the tolerated output current ripple. The required value of L1 is inversely proportional to the ripple current  $\Delta I_O$  in it.

$$L1 = (V_O \cdot T_{OFF}) / \Delta I_O \tag{1}$$

where  $V_O$  is the forward voltage of the LED string.  $T_{OFF}$  is the off-time of the An9920A. The output current in the LED string ( $I_O$ ) is calculated then as:

$$I_O = I_{TH} \eqno(2)$$

(instead of the expression:  $I_O {=} I_{TH} \mbox{ } {-}\Delta I_O/2$  for An9922)

where  $I_{TH}$  is the current sense comparator threshold. Thus, at present, the ripple current is not introduces a peak-to-average error in the output current setting that no needs to be accounted for. Due to average logic, the output current is independent on the L1 and  $V_O$  values at the wide range. The ripple current is varied only. Due to the constant off-time control technique used in the An9920A, the ripple current is independent of the input AC or DC line voltage variation. Therefore, the output average current will remain unaffected by the varying input voltage, the inductance value and the LED quantity.

Adding a filter capacitor across the LED string can reduce the output current ripple even further, thus permitting a reduce value of L1.

Another important aspect of designing an LED driver with the An9920A is related to certain parasitic elements of the circuit, including distributed coil capacitance of L1, junction capacitance and reverse recovery of the rectifier diode D1, capacitance of the printed circuit board traces C<sub>PCB</sub> and output capacitance C<sub>DRAIN</sub> of the controller itself. These parasitic elements affect the efficiency of the switching converter and could potentially cause false triggering of the current sense comparator if not properly managed. Minimizing these parasitics is essential for efficient and reliable operation of the An9920A.

Coil capacitance of inductors is typically provided in the manufacture's data books either directly or in terms of the self-resonant frequency (SRF).

$$SRF = 1 / (2\pi \cdot \sqrt{(L \cdot C_L)})$$

where L is the inductance value, and  $C_L$  is the coil capacitance. Charging and discharging this capacitance every switching cycle causes high-current spikes in the LED string. Therefore, connecting a small capacitor  $C_O$  (~10nF) is recommended to bypass these spikes.

Using an ultra-fast rectifier diode for D1 is recommended to achieve high efficiency and reduce the risk of false triggering of the current sense comparator. Using diodes with shorter reverse recovery time  $t_{\rm rr}$  and lower junction capacitance  $C_{\rm J}$  achieves better performance. The reverse voltage rating  $V_R$  of the diode must be greater than the maximum input voltage of the LED lamp.

The total parasitic capacitance present at the DRAIN pin of the An9920A can be calculated as:

$$C_{P} = C_{DRAIN} + C_{PCB} + C_{L} + C_{J}$$

(3)

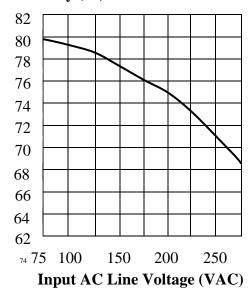

When the switching MOSFET turns on, the capacitance  $C_P$  is discharged into the DRAIN pin of the IC. The discharge current is limited to about 210mA typically. However, it may become lower at increased junction temperature. The duration of the leading edge current spike can be estimated as:

$$T_{SPIKE} = [(V_{IN} \cdot C_P) / (I_{SAT})] + t_{rr}$$

(4)

In order to avoid false triggering of the current sense comparator, C<sub>P</sub> must be minimized in accordance with the following expression:

$$C_{P} < I_{SAT} \cdot (T_{BLANK(MIN)} - t_{rr}) / V_{IN(MAX)}$$

(5)

where  $T_{BLANK(MIN)}$  is the minimum blanking time of 200ns, and  $V_{IN(MAX)}$  is the maximum instantaneous input voltage.

#### **Estimating Power Loss**

Discharging the parasitic capacitance CP into the DRAIN pin of the An9920A is responsible for the bulk of the switching power loss. It can be estimated using the following equation:

$$\mathbf{P}_{\text{SWITCH}} = \left[ \left( \mathbf{V}_{\text{IN}}^2 \cdot \mathbf{C}_{\text{P}} / 2 \right) + \mathbf{V}_{\text{IN}} \cdot \mathbf{I}_{\text{SAT}} \cdot \mathbf{t}_{\text{rr}} \right] \cdot \mathbf{F}_{\text{S}}$$

(6)

where  $F_S$  is the switching frequency,  $I_{SAT}$  is the saturated DRAIN current of the An9920A. The switching loss is the greatest at the maximum input voltage. The switching frequency is given by the following:

$$\mathbf{F_S} = (\mathbf{V_{IN}} - \boldsymbol{\eta}^{-1} \cdot \mathbf{V_O}) / \mathbf{V_{IN}} \cdot \mathbf{T_{OFF}}$$

(7)

where  $\eta$  is the efficiency of the power converter.

When the An9920A LED driver is powered from the full-wave rectified AC input, the switching power loss can be estimated as:

$$P_{SWIYCH} \approx [1/(2 \cdot T_{OFF})] \cdot (V_{AC} \cdot C_P + 2 \cdot I_{SAT} \cdot t_{rr}) \cdot$$

$$\cdot (V_{AC} - \eta^{-1} \cdot V_O) \tag{8}$$

V<sub>AC</sub> is the input AC line voltage.

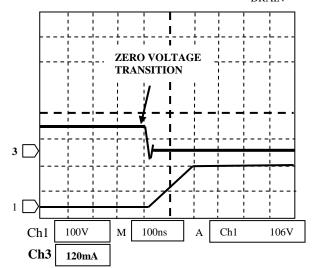

The switching power loss associated with turn-off transitions of the DRAIN pin can be disregarded. Due to the large amount of parasitic capacitance connected to this switching node, the turn-off transition occurs essentially at zero- voltage. Conduction power loss in the An9920A can be calculated as:

$$P_{COND} = (D \cdot I_0^2 \cdot R_{ON}) + (I_{DD} \cdot V_{IN} \cdot (1 - D))$$

(9)

where  $\mathbf{D} = \mathbf{V_O}$  /  $(\eta \cdot \mathbf{V_{IN}})$  is the duty ratio,  $R_{ON}$  is the on-resistance,  $I_{DD}$  is the internal linear regulator current.

When the LED driver is powered from the full-wave rectified AC line input, the exact equation for calculating the conduction loss is more cumbersome. However, it can be estimated using the following equation:

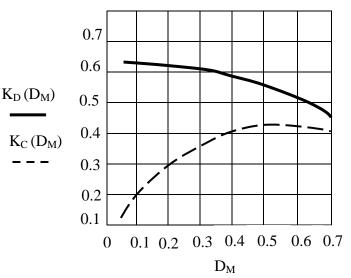

$$\mathbf{P}_{\text{COND}} = (\mathbf{K}_{\mathbf{C}} \cdot \mathbf{I_0}^2 \cdot \mathbf{R}_{\mathbf{ON}}) + (\mathbf{K}_{\mathbf{D}} \cdot \mathbf{I}_{\mathbf{DD}} \cdot \mathbf{V}_{\mathbf{AC}}) \quad (10)$$

where  $V_{AC}$  is the input AC line voltage. The coefficients  $K_C$  and  $K_D$  can be determined from the minimum duty ratio of the An9920A.

Fig.1. Conduction Loss Coefficients  $\mathbf{K}_C$  and  $\mathbf{K}_D$  EMI Filter

As with all off-line converters, selecting an input filter is critical to obtaining good EMI. A switching side capacitor, albeit of small value, is necessary in order to ensure low impedance to the high frequency switching current of the converter. As a rule of thumb, this capacitor should be approximately 0.1 -  $0.2\mu F/W$  of LED output power. A recommended input filter is shown in Figure 2 for the following design example.

#### **Design Example**

Let us design an An9920A LED lamp driver meeting the following specification:

Input: Universal AC, 85-135VAC

Output Current: 100mA

Load: String of 12 LED (Power TOPLED

$OSRAM^{\otimes} V_F = 2.5V \text{ max. each})$

#### **Step 1.** Calculation L1.

The output voltage  $V_O = 12 \times V_F = 30V$  (max.). Use equation (1) assuming a 15% peak-to-peak ripple.

$L1 = (30V \cdot 11.5 \mu s) / (0.15 \cdot 100 mA) = 23 mH$

Select L1= 22mH, I = 120mA. Typical SRF = 270KHz. Calculate the coil capacitance.

$C_L = 1 / [L1 \cdot (2\pi \cdot SRF)^2] = 1 / [22mH \cdot (2\pi \cdot 270KHz)^2] \approx 15pF$

#### Step 2. Selecting D1.

Select D1 MUR160 with  $V_R = 600V$ ,  $trr \approx 50$ ns and  $C_I \approx 8pF$  ( $V_F > 50V$ ).

**Step 3.** Calculating total parasitic capacitance using (3).

$$C_P = 5pF + 5pF + 15pF + 8pF = 33pF$$

**Step 4.** Calculating the leading edge spike duration using (4), (5).

$T_{SPIKE}$  =  $(135V \cdot \sqrt{2} \cdot 33pF) / 150mA + 50ns \approx 92ns < <math>T_{BLANK(MIN)}$  = 200ns

**Step 5.** Estimating power dissipation in An9920A at 135VAC using (8) and (10).

Let us assume that the overall efficiency  $\eta = 0.7$ .

#### **Switching Power Loss**

$P_{\text{SWITCH}} = (135\text{V} \cdot 33\text{pF} + 2 \cdot 150\text{mA} \cdot 50\text{ns}) \cdot (135\text{V} - 30\text{V}/0.7) / (2 \cdot 11.5\mu\text{s}) \approx 80\text{mW}$

#### **Minimum Duty Ratio**

$D_{\rm M} = 30 \text{V} / (0.7 \cdot 135 \text{V} \cdot \sqrt{2}) \approx 0.23$

#### **Conduction Power Loss**

$P_{COND} = 0.32 \cdot (100 \text{mA})^2 \cdot 100 \Omega + 0.62 \cdot 220 \mu \text{A} \cdot 135 \text{V} \approx 340 \text{mW}$

#### **Total Power Dissipation in An9920A:**

$P_{TOTAL} = 80 \text{mW} + 340 \text{mW} = 420 \text{mW}$

**Step 6.** Selecting input capacitor C<sub>IN</sub>

Output Power =  $30V \cdot 100mA = 3W$

Select  $C_{IN} = 0.47 \mu F$ , 250V

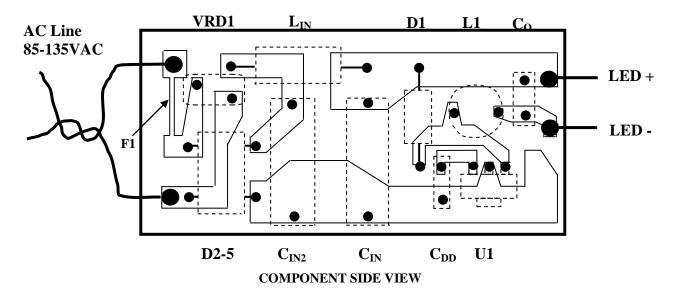

Figure 2. Universal 85 - 135VAC LED Lamp Driver

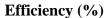

Figure 3. Typical Efficiency

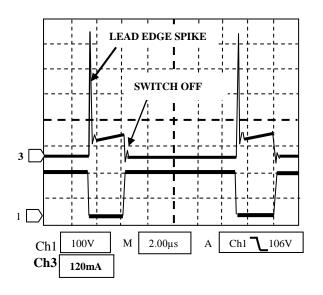

**Figure 5.** Lead Edge Spike Ch1: V<sub>DRAIN</sub>, Ch3: I<sub>DRAIN</sub>

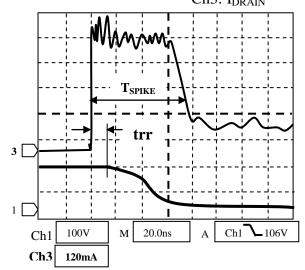

**Figure 4.** Switch-On-Off Transition. Ch1: V<sub>DRAIN</sub>, Ch3: I<sub>DRAIN</sub>

**Figure 6.** Switch-Off Transition. Ch1: V<sub>DRAIN</sub>, Ch3: I<sub>DRAIN</sub>

**Functional Block Diagram**

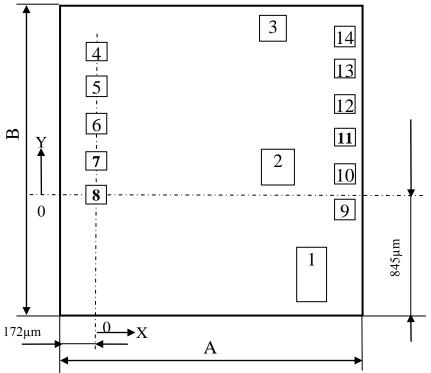

## **Pad Diagram**

- 1. Chip size: A=1.26mm, B=1.59mm (without scribe line width).

- 2. Scribe line width: X=80μm, Y=80μm

- 3. Pad size: Pad 1: 101μm x 202μm

Pad 2: 125μm x 165μm Pad 3: 100μm x 100μm

Pad 4÷Pad 14: 90µm x 90µm

Pad 4-Pad 14: 90μm x 90μm

- 4. Substrate to GND.

- 5. Wafer thickness: 460 μm

## **Pad Description and Location**

| №<br>Pad | Symbol       | Description                                                                                         | Х<br>( мкм) | Ү<br>( мкм) |

|----------|--------------|-----------------------------------------------------------------------------------------------------|-------------|-------------|

| 1        | DRAIN        | Switching MOSFET Drain Output and Linear<br>Regulator Input                                         | 883         | -554        |

| 2        | GND          | Common Connection for all Circuits                                                                  | 712         | 130         |

| 3        | $V_{DD}$     | Power Supply Pin for Internal Control Circuit. Bypass this pin with a 0.1µF low impedance capacitor | 692         | 638         |

| 4        | $V_{ m REF}$ | Reference Voltage Output, Test Pad                                                                  | 0           | 520         |

| 5        | GND1         | Ground Input for $V_{\text{REF}}$ trimming,<br>Test Pad                                             | 0           | 390         |

| 6        | F0           | V <sub>REF</sub> Trimming Least Significant Input, Test Pad                                         | 0           | 260         |

| 7        | F1           | V <sub>REF</sub> Trimming Middle Significant Input, Test pad                                        | 0           | 130         |

| 8        | F2           | V <sub>REF</sub> Trimming Most Significant Input, Test Pad                                          | 0           | 0           |

| 9        | S            | Switching MOSFET Source Output,<br>Test Pad                                                         | 983         | -21         |

| 10       | F5           | I <sub>TH</sub> Trimming Most Significant Input, Test Pad                                           | 983         | 109         |

| 11       | F4           | I <sub>TH</sub> Trimming Middle Significant Input, Test Pad                                         | 983         | 239         |

| 12       | F6           | I <sub>TH</sub> Trimming Common Input, Test Pad                                                     | 983         | 369         |

| 13       | F3           | I <sub>TH</sub> Trimming Least Significant Input, Test Pad                                          | 983         | 499         |

| 14       | G            | Gate Input, Test Pad                                                                                | 983         | 629         |

#### **An9920A Layout Considerations**

See Figure 7 for a recommended circuit board layout for the An9920A.

#### **Single Point Grounding**

Use a single point ground connection from the input filter capacitor to the area of copper connected to the GND pin.

#### Bypass Capacitor (C<sub>DD</sub>)

The V<sub>DD</sub> pin bypass capacitor C<sub>DD</sub> should be located as near as possible to the V<sub>DD</sub> and GND pins.

#### **Switching Loop Areas**

The area of the switching loop connecting the input filter capacitor  $C_{IN}$ , the diode D1 and the An9920A together should be kept as small as possible.

The switching loop area connecting the output filter capacitor C<sub>0</sub>, the inductor L1 and the diode D1 together should be kept as small as possible.

#### Thermal Considerations vs. Radiated EMI

The cooper area where GND pin is connected acts not only as a single point ground, but also as a heat sink.

This area should be maximized for good heat sinking, especially when An9920A (SOT-89 package), is used.

The same applies to the cathode of the free-wheeling diode D1. Both nodes are quiet and therefore, will not cause radiated RF emission. The switching node copper area connected to the DRAIN pin of the An9920A, the anode of D1 and the inductor L1 needs to be minimized. A large switching node area can increase high frequency radiated EMI.

#### **Input Filter Layout Considerations**

The input circuit of the EMI filter must not be placed in the direct proximity to the inductor L1 in order to avoid magnetic coupling of its leakage fields. This consideration is especially important when unshielded construction of L1 is used. When an axial input EMI filter inductor  $L_{\rm IN}$  is selected, it must be positioned orthogonal with respect to L1. The loop area formed by  $C_{\rm IN2}$ ,  $L_{\rm IN}$ , and  $C_{\rm IN}$  should be minimized. The input lead wires must be twisted together.

Figure 7. Recommended circuit board layout with the An 9920A (SOT-89 package)