# SIMetrix/SIMPLIS V7.2 新特性

SIMetrix/SIMPLIS V7.2 正式发布,其主要新特性如下:

### (一) 波形查看和探头的新特性 (SIMetrix 和 SIMPLIS)

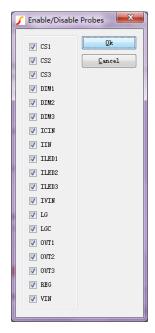

▶ 探头使能设置:统一编辑探头是否使能, Probe | Enable/Disable Fixed Probes...

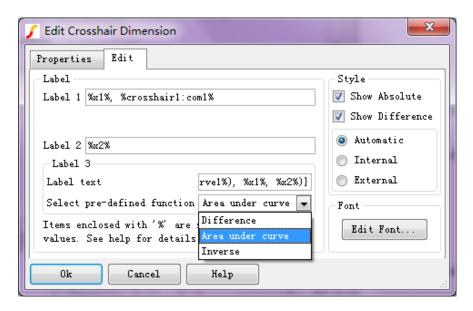

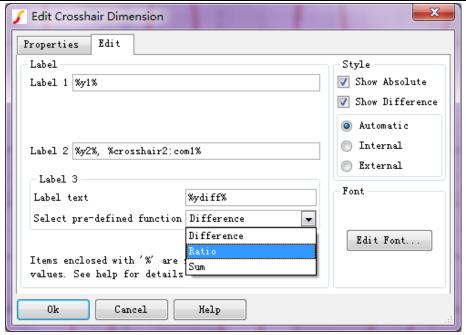

光标测量:添加了新的光标测量量,其中横坐标:面积和倒数,纵坐标:比率和加法

- ▶ 固定的 XY 探头:可在原理图上放置固定的 XY 探头 , Probe | Place XY Probe

- > 积分微分菜单:在波形窗口增加了积分和微分处理功能, Plot | Plot Integral and Plot | Plot Differential

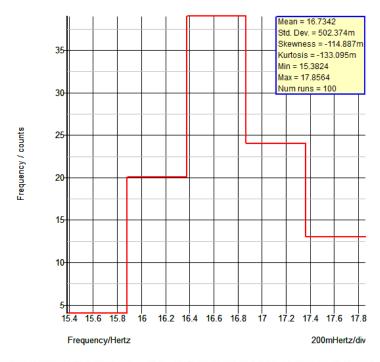

- 柱状图:在命令栏中输入 Set HistoAdvancedStats 可在柱状图结果中增加峰度和偏度测量值

## (二) 工具菜单 (SIMetrix 和 SIMPLIS)

SIMetrix/SIMPLIS V7.1 中的 Post-Process 菜单改成 Tools 菜单,并增加了 Load Component Values 和 Power Report 功能。

#### ▶ 加载器件值

该功能可帮助用户快速更改元器件值,而不用逐一编辑每一个器件。例如,采用同一个原理图的设计时,可以保存一个配置文件,包含一组器件值,每一个设计都可以通过加载该配置文件来统一给元器件赋值。配置完成后,会生成一份文档:

| Load component value Started @ 10:08:51 |             |       |       |  |

|-----------------------------------------|-------------|-------|-------|--|

| Action:                                 | refdes      | old   | new   |  |

|                                         |             |       |       |  |

| No Change                               | Vin.VC      | 12    | 12    |  |

| No Change                               | Vin.ESR     | 1m    | 1m    |  |

| Change                                  | C5.CC       | 22u   | 4.7u  |  |

| No Change                               | C6.CC       | 1u    | 1u    |  |

| No Change                               | C10.CC      | 100n  | 100n  |  |

| No Change                               | C11.CC      | 1u    | 1u    |  |

| Change                                  | L1.LI       | 1.8u  | 4.2u  |  |

| No Change                               | C7.CC       | 22u   | 22u   |  |

| Change                                  | C7.QUANTITY | 2x    | 2     |  |

| No Change                               | C9.CC       | 1p    | 1p    |  |

| Change                                  | R1.VALUE    | 40.2k | 59k   |  |

| Change                                  | R2.VALUE    | 12.7k | 19.1k |  |

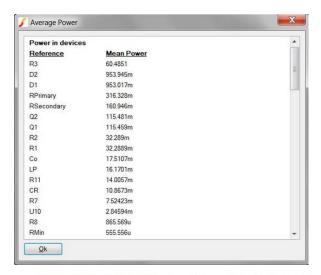

### ▶ 功率报告(SIMetrix 和 SIMPLIS)

计算每个元件的功率并生成报告。

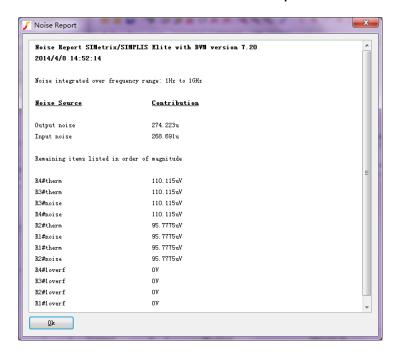

### ▶ 噪声报告(SIMetrix)

Noise 分析仿真结束后,通过 Tools/Reports/Noise Report 生成报告。

# (三) POP Trigger 可放置于各层原理图

SIMetrix/SIMPLIS V7.2 可以将 POP Trigger 放在任一层的原理图上,而旧版本只能放在顶层原理图中,且只能放一个,否则会报错并停止运行。

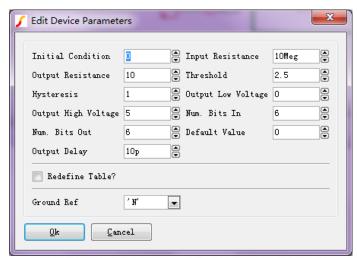

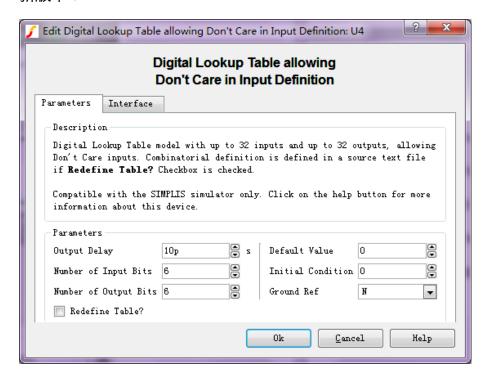

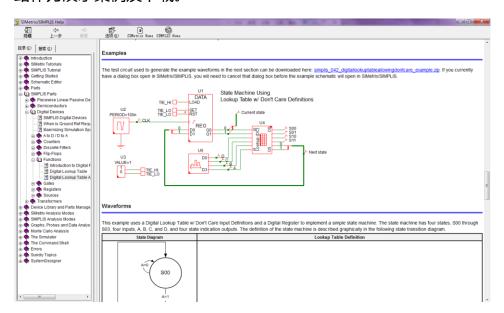

# (四) SIMPLIS 数字器件库的新对话框和帮助文档

SIMPLIS 中的数字器件库中的器件都有新的参数编辑对话框,例如数字查找表。

#### 旧版本:

#### 新版本:

SIMetrix/SIMPLIS V7.2 的帮助文档不仅增加了数字器件的详细说明,并且提供了近百个电路作为演示案例及下载。

# (五) 其他特性(SIMetrix 和 SIMPLIS)

▶ 模型库错误处理改进:当安装模型文件时,在命令窗口会显示遇到的错误信息,帮助用户判断模型的错误信息。

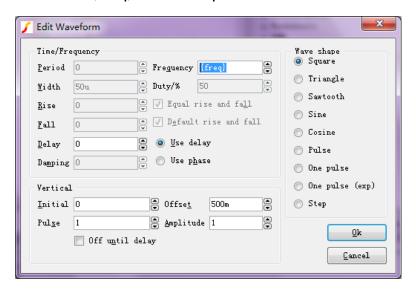

▶ 波形发生器可接受参数定义:可在原理图中对波形发生器定义参数,如可以在定义频率 时输入{freq},使用 freq 这个参数来设置频率值,此特性不兼容旧版本。

#### (六) SIMPLIS 其他特性

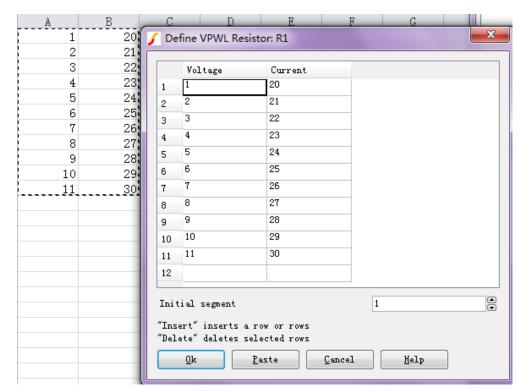

> SIMPLIS 的 PWL 元件增加了可以直接将 Excel 表格中的数据直接粘贴的功能。

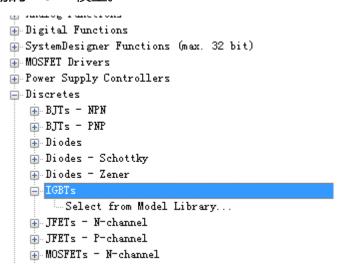

▶ 增加了 IGBT 模型。

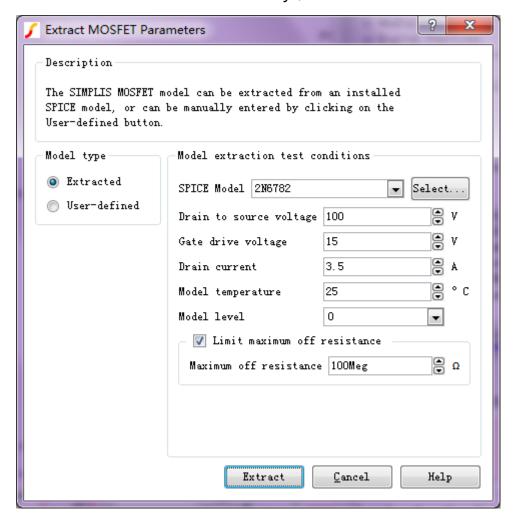

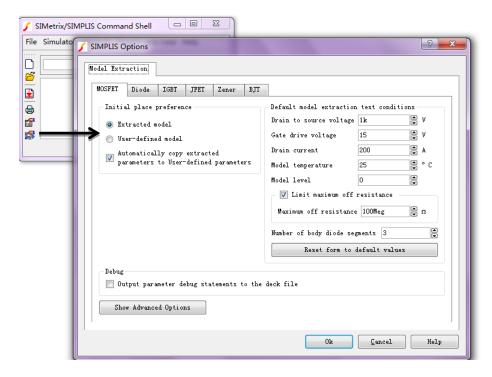

增加了模型提取功能和用户自定义器件参数功能,目前支持该功能的有 MOSFETs、

Diodes、BJTs、IGBTs、JFETs、Schottky和 Zener diodes。

▶ 增加了模型提取设置窗口。

➤ SIMPLIS 新增功能模块——SystemDesigner

SystemDesigner 是 SIMPLIS 公司为数字系统仿真开发的一个功能模块,它是一组由 SIMPLIS 中的 building blocks 构成,用于电力电子系统中的数字控制建模。通常这些系统中包含有硬件和软件的数字控制,如微控制器,DSPs,FPGAs。其主要特点有:

- 数字控制系统中时间采样的数据支持 32 位有符号整数和双精度浮点数两种,采用离散 采样控制信号的方式精确模拟时间采样系统中的移相效果;

- 整数数据精确描绘实际产品执行时的量化误差;

- 双精度浮点数数据用模拟的精度描绘信号通路的大小,本质上可消除任何的量化误差;

- 用双精度浮点数建模时间采样的信号通路的主要优势在于可以使用 SIMPLIS 中的 POP

和 AC 分析数字控制系统,显著提高仿真速度和精度;

- 信号通路中的每一个操作,如加法、乘法、移相等,用户都可以自定义其时钟周期的个数,模拟软件代码;

- 时钟信号可分布于原理图的所有层中,简化时钟连线;

- 提供基于 TI 公司的 Piccolo enhanced PWM (ePWM) 模块作为 PWM 发生器。

- 1) 这个 PWM 模块可以产生几乎任何的 PWM 样式,包括变频(LLC)和移相的拓扑;

- 2) 这个 PWM 发生器可以在 PWM 周期内的任一点开始进行 ADC 转换。

注:仅 Pro 版和 Elite版 license 包含 SystemDesigner 模块 (详见附录)。

-----

附录:软件模块功能对照表

|                                                                   | SIMetrix/SIMPLIS | SIMetrix/SIMPLIS<br>Pro | SIMetrix/SIMPLIS<br>Elite |  |  |

|-------------------------------------------------------------------|------------------|-------------------------|---------------------------|--|--|

| SIMetrix Simulation Package                                       | √                | √                       | ✓                         |  |  |

| SIMPLIS Simulator                                                 | √                | √                       | √                         |  |  |

| Additional features available for SIMetrix and SIMPLIS simulators |                  |                         |                           |  |  |

| Multi-core support<br>(up to 4 cores)                             | ×                | √                       | √                         |  |  |

| Multi-core support<br>(up to 16 cores)                            | ×                | ×                       | ✓                         |  |  |

| DVM Design Verification Module                                    | option           | option                  | option                    |  |  |

| Additional features available for the SIMPLIS simulator           |                  |                         |                           |  |  |

| SystemDesigner                                                    | ×                | √                       | <b>✓</b>                  |  |  |

| Additional features available for the SIMetrix simulator          |                  |                         |                           |  |  |

| Verilog-A                                                         | ×                | √                       | √                         |  |  |

| Verilog-HDL                                                       | ×                | √                       | <b>✓</b>                  |  |  |

| Basic IC Design features                                          | ×                | √                       | √                         |  |  |

| Advanced IC design features                                       | ×                | ×                       | √                         |  |  |

| Real time noise                                                   | ×                | ×                       | √                         |  |  |